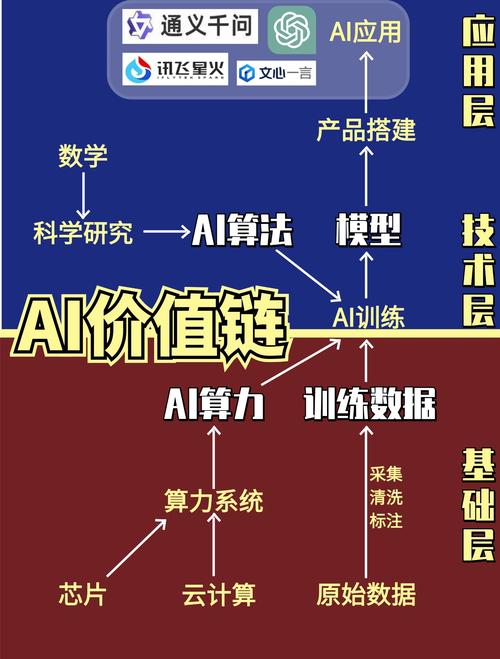

可以把AI芯片想象成一种专门为“数学计算”而生的超级计算机,与我们日常使用的通用CPU(中央处理器)有很大不同。

为了理解它的原理,我们首先需要明白AI,特别是深度学习,到底在做什么。

第一步:理解AI计算的本质

AI模型(尤其是深度神经网络)的核心工作可以分解为两个主要操作:

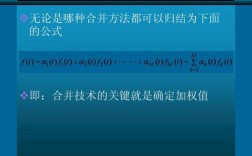

- 大量的乘加运算:这是最核心、最消耗计算资源的部分,想象一下,神经网络由无数个“神经元”组成,每个神经元都会接收来自上一层神经元的输入,然后将这些输入值乘以各自的“权重”(Weight),再把所有乘积加起来,最后通过一个“激活函数”(Activation Function)得到输出,一个复杂的模型可能需要执行数万亿甚至更多的这类乘加运算。

- 大量的数据搬运:模型中的权重、输入数据、中间结果等都需要在内存(存储)和计算单元之间频繁地移动,数据搬运的耗时往往比计算本身还要长。

AI计算的特点是“计算密集型”和“数据密集型”,并且其计算模式高度规整、重复。

第二步:通用CPU的瓶颈

我们电脑里的CPU(Intel, AMD)是一个“多面手”,设计目标是能够快速处理各种不同的任务,比如操作系统调度、运行软件、玩游戏等,它擅长逻辑判断、分支跳转等复杂操作。

对于AI这种“简单但重复”的乘加运算,CPU就显得有些“大材小用”且效率不高了:

- 指令集复杂:CPU为了处理通用任务,其指令集非常复杂,执行一条指令需要多个时钟周期,而AI的乘加运算其实可以简化为一条指令。

- 架构不适合并行:CPU虽然有多个核心,但其核心设计并不适合同时处理海量的、相同的数据,它更擅长处理需要“思考”的串行任务。

这就好比让一位世界顶级的脑外科医生去流水线上拧螺丝,虽然他手很巧,但效率远不如专门设计来拧螺丝的机器。

第三步:AI芯片的核心设计原理

AI芯片的设计初衷就是为了解决CPU的瓶颈,专门为上述的AI计算特点而优化,其核心原理可以概括为以下几点:

架构革命:从“通用”到“专用”

AI芯片采用的是ASIC(专用集成电路)或高度定制的SoC(片上系统)架构,这意味着它不是为了通用计算而设计的,而是为AI这个特定场景量身定做的。

- 代表架构:SIMT(单指令多线程)

- 这是NVIDIA GPU(图形处理器)采用的架构,也是目前AI训练领域最主流的架构,它的核心思想是:用一个指令,同时去处理多个数据。

- 这就像一个老师(指令)对着全班几十个学生(数据)同时喊一句“起立”,所有人都执行了同一个动作,这对于AI中大量重复的计算(比如同时对矩阵中的所有元素做乘法)效率极高。

- GPU中包含成百上千个“流处理器核心”,它们可以被组织成多个“流式多处理器”,每个SM可以同时管理成百上千个线程,这就是“多线程”的由来。

核心计算单元:高度并行的计算阵列

为了高效执行乘加运算,AI芯片内部设计了大量的并行计算单元,这些单元被组织成一个或多个巨大的“计算阵列”或“张量核心”(Tensor Core)。

- 张量核心:这是NVIDIA在Volta架构之后引入的“核中核”,专门用于加速矩阵乘法,一个简单的3x3矩阵乘法,在传统GPU上可能需要多个步骤完成,而张量核心可以在一个时钟周期内直接完成,效率呈数量级提升。

- 脉动阵列:这是Google TPU(张量处理单元)采用的核心技术,它就像一个“计算流水线”,数据像血液一样按照固定的节奏“脉动”流过阵列中的各个计算单元,数据在流动中被处理,极大地减少了数据搬运的开销,非常适合处理卷积神经网络等特定算法。

内存墙的突破:高带宽内存与片上缓存

前面提到,数据搬运是AI计算的瓶颈,AI芯片通过多种创新技术来解决这个问题,统称为“存算一体”或“近数据计算”的思想。

- 高带宽内存:AI芯片通常会搭配专门的HBM内存,它将很多个DRAM芯片堆叠在一起,并与芯片通过超宽的接口直接连接,就像给CPU接上了“高速公路”,而不是普通的“乡间小路”,从而实现了极高的数据传输带宽。

- 庞大的片上缓存:在芯片内部,SRAM缓存被做得非常大,这样可以尽可能多地让计算所需的数据和权重都放在缓存里,避免频繁地、缓慢地从外部HBM内存中读取数据,就像把最常用的工具都放在手边的工具箱里。

- 片上内存:一些芯片(如TPU)还集成了大容量的片上SRAM,作为中间计算的“草稿纸”,进一步减少对外部内存的访问。

精度优化:低精度计算

AI模型在训练和推理时,并不需要像CPU那样使用32位甚至64位的浮点数(FP32),研究表明,使用16位浮点数(FP16)甚至8位整数(INT8)甚至4位(INT4)进行计算,对模型的最终精度影响很小,但能带来巨大的性能提升和功耗降低。

- 原理:数字位宽越小,表示一个数值所需的存储空间就越小,数据搬运量也随之减少,芯片可以用更少的晶体管来实现低精度的乘加运算,计算速度更快,功耗也更低。

- 硬件支持:现代AI芯片从硬件层面就原生支持FP16、INT8、INT4等低精度计算,并提供专门的指令集来加速。

专用硬件加速:超越MAC

除了基础的乘加运算,AI芯片还集成了专门用于处理特定AI操作的硬件模块。

- 激活函数单元:像ReLU(修正线性单元)这样的激活函数,其计算非常简单(max(0, x)),AI芯片会设置专门的硬件电路,用一个时钟周期就完成它,而不是调用一个软件函数。

- 归一化层:如Layer Normalization、Batch Normalization等,也有专门的硬件单元来加速。

- 转置/池化单元:这些在神经网络中常见的操作也有专门的硬件支持。

第四步:AI芯片的典型工作流程

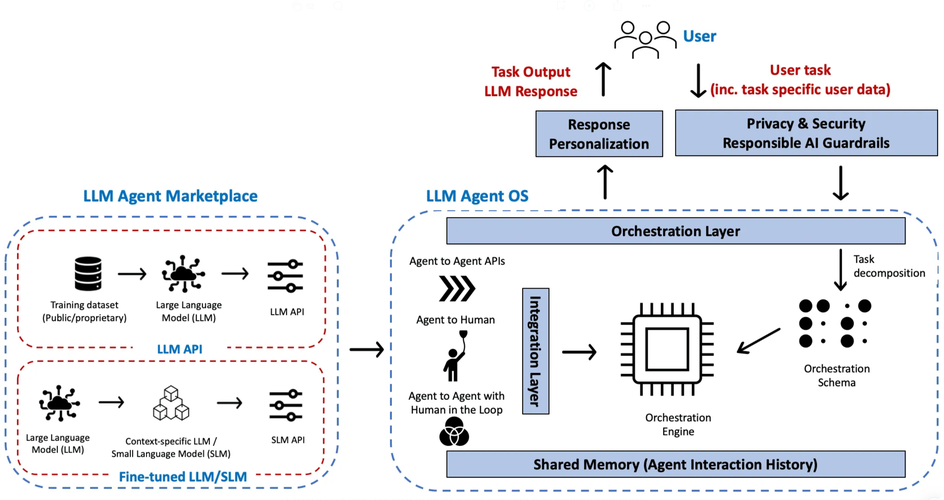

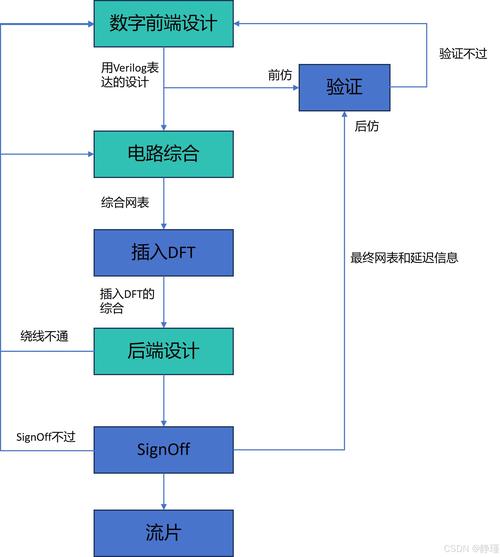

一个AI芯片在运行一个AI模型时,大致会经历以下步骤:

- 模型编译:将高级的AI框架(如TensorFlow, PyTorch)编写的模型,通过编译器(如NVIDIA的CUDA, Google的XLA)转换成芯片能够理解的底层指令和操作序列。

- 数据加载:将模型的权重和输入数据从外部存储(如硬盘)加载到高速的HBM内存中。

- 数据调度:芯片的控制器从HBM中取出数据和权重,并将其放入片上缓存或直接分配给计算阵列。

- 并行计算:计算阵列(如SIMT核心或脉动阵列)开始执行海量的乘加运算、激活函数等操作,成千上万的计算核心同时工作。

- 结果回写:计算出的中间结果和最终结果被写回HBM或片上缓存,可能用于下一层的计算,或者最终输出。

AI芯片 vs. 通用CPU

| 特性 | AI芯片 (如GPU, TPU) | 通用CPU (如Intel, AMD) |

|---|---|---|

| 设计目标 | 专用加速,针对AI/ML/GPU计算 | 通用计算,处理各种任务 |

| 核心架构 | 大规模并行SIMT/脉动阵列 | 少量高性能核心,擅长乱序执行 |

| 计算单元 | 成百上千个简单核心 | 少量(几到几十个)复杂核心 |

| 内存访问 | 高带宽内存,庞大缓存,近数据计算 | 较低带宽内存,缓存相对较小 |

| 数据精度 | 原生支持低精度计算(FP16, INT8) | 主要支持高精度计算(FP32, FP64) |

| 功耗效率 | 极高(每瓦特性能远超CPU) | 相对较低 |

| 灵活性 | 低(只能跑特定类型的负载) | 高(可运行任何软件) |

一句话概括AI芯片的基本技术原理:

通过高度并行化的专用计算架构、突破性的内存技术、低精度计算优化以及针对AI操作的硬件加速,AI芯片将AI计算中占主导地位的、海量重复的乘加运算效率提升到了传统CPU无法企及的高度,从而实现了对AI任务的快速赋能。