高速实时信号处理技术是现代信息系统的核心支撑技术之一,它致力于对连续产生的信号进行即时采集、分析与处理,以满足系统对低延迟、高吞吐量和强可靠性的苛刻要求,该技术广泛应用于雷达、通信、医疗影像、工业自动化、自动驾驶等领域,成为推动科技进步和产业升级的关键驱动力。

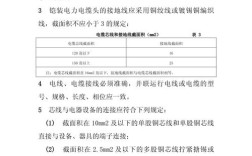

高速实时信号处理的核心在于“实时性”与“高速度”的统一,实时性要求系统必须在规定的时间内完成信号的处理任务,否则将导致结果失效;高速度则要求处理系统能够应对高频采样产生的海量数据流,为实现这一目标,技术体系通常包含信号采集、高速传输、实时处理和结果输出四个关键环节,在信号采集环节,高速模数转换器(ADC)是核心器件,其采样率和分辨率直接决定了系统可处理信号的上限频率和动态范围,高性能ADC的采样率已突破GHz级别,配合低噪声放大器和高抗干扰设计,确保了原始信号的保真度。

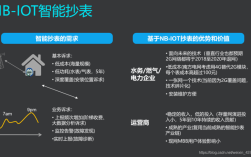

数据传输环节是连接采集与处理的桥梁,其带宽和延迟直接影响整体性能,传统的并行总线传输方式在高速场景下面临布线复杂、时钟偏移等问题,而基于SerDes(串行器/解串器)技术的串行传输方案,如PCIe、Thunderbolt等,凭借其高带宽、低延迟和易于扩展的优势,成为主流选择,在FPGA或SoC芯片内部,高速的片上网络(NoC)和专用的DMA控制器,则实现了数据在采集模块、处理模块和存储模块之间的高效流转,避免数据瓶颈。

实时处理环节是技术体系的灵魂,其架构设计直接决定了处理能力,早期系统多依赖通用DSP(数字信号处理器)进行算法实现,但面对5G通信、雷达阵列等超大规模并行计算需求,通用DSP的并行处理能力逐渐显现不足,为此,基于FPGA的可重构计算和基于GPGPU的大规模并行计算成为新的发展方向,FPGA通过硬件描述语言直接映射算法逻辑,具有极低的延迟和极高的能效比,特别适合I/O密集型和确定性要求高的任务;而GPGPU则凭借数千个计算核心,在矩阵运算、深度学习等复杂算法上展现出强大的吞吐量优势,近年来,异构计算架构,如“CPU+FPGA+GPU”的组合,通过任务分工,实现了性能与灵活性的最佳平衡。

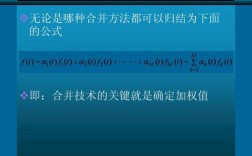

软件算法层面,实时信号处理依赖高效的算法库和编程模型,针对FFT(快速傅里叶变换)、FIR滤波、波束形成等经典算法,研究者们不断探索优化方法,如基-2/基-4 FFT、分布式算法、脉动阵列结构等,以减少计算量和内存访问次数,在编程模型上,OpenCL、CUDA等异构编程框架,允许开发者统一管理CPU、GPU、FPGA等不同计算资源,简化了跨平台开发的难度,自适应算法和动态功耗管理技术的引入,使系统能够根据信号环境和任务负载,动态调整处理策略,在保证实时性的前提下实现能效最优化。

为了更直观地对比不同处理平台的特点,以下是一个简要的表格:

| 处理平台 | 优势 | 劣势 | 典型应用场景 |

|---|---|---|---|

| 通用DSP | 开发周期短,生态系统成熟,浮点性能强 | 并行能力有限,灵活性不及FPGA | 通信基带处理、音频处理 |

| FPGA | 极低延迟,硬件级并行,可重构,高能效 | 开发难度大,设计周期长,成本高 | 雷达信号处理、高速接口协议转换 |

| GPGPU | 超高吞吐量,适合大规模并行计算 | 功耗较高,延迟相对较高,编程复杂 | 深度学习推断、科学计算 |

高速实时信号处理技术还面临诸多挑战,如如何在保证实时性的前提下处理非平稳信号和未知干扰,如何在高采样率下实现多通道数据的同步与关联,以及如何构建高可靠、容错的系统架构等,未来的发展趋势将聚焦于更高性能的ADC/DAC技术、更先进的3D集成芯片、更智能的AI辅助算法优化,以及面向6G通信、量子计算等前沿领域的专用处理系统,持续拓展人类感知和处理物理世界信息的边界。

相关问答FAQs:

Q1: 高速实时信号处理中的“实时”具体指什么?如何衡量一个系统是否满足实时性要求? A1: 在高速实时信号处理中,“实时”并非指处理速度无限快,而是指系统的处理延迟必须小于或等于某个预定的截止期限,这个截止期限由应用场景决定,在汽车防碰撞雷达中,处理延迟可能需要控制在毫秒甚至微秒级别,以确保有足够的时间进行制动决策,衡量一个系统是否满足实时性要求,主要看其在最坏情况下的处理延迟是否始终小于截止期限,这需要通过严格的性能分析和测试来验证,包括测量从信号输入到结果输出的端到端延迟,并分析其在不同负载和数据模式下的延迟分布,确保其具有确定性,即延迟不会出现不可预测的抖动。

Q2: 为什么说FPGA是高速实时信号处理领域的理想选择,它相比传统DSP有哪些核心优势? A2: FPGA之所以成为高速实时信号处理的理想选择,核心优势在于其硬件可重构性和天然的并行处理能力,传统DSP是基于冯·诺依曼架构的串行处理器,其性能提升受限于时钟频率和指令流水线,而FPGA内部包含大量可配置的逻辑单元(LUT)和硬件乘法器,开发者可以将特定的算法(如一个FIR滤波器或一个FFT蝶形运算)直接“固化”为硬件电路,实现算法与硬件的深度匹配,这种“硬件即算法”的方式,消除了指令译码和取指等开销,延迟极低,FPGA可以创建成百上千个并行的处理单元,同时对多个数据流进行处理,吞吐量远超单核或多核DSP,FPGA的I/O引脚丰富且可自定义,能够直接与高速ADC/DAC连接,简化了系统设计,在延迟敏感、高带宽、需要硬件级定制的场景下,FPGA的性能和灵活性是传统DSP难以比拟的。