zc706技术文档涵盖了该开发板的核心特性、硬件架构、接口资源及开发环境搭建等关键信息,为开发者提供了全面的技术参考,以下从硬件平台概述、核心模块详解、接口资源分布、开发环境配置及典型应用场景五个维度展开说明。

zc706是基于Xilinx Kintex-7系列FPGA(XC7K325T-2FFG676C)的高性能开发板,专为数字信号处理、逻辑验证及原型设计打造,板载资源包括1GB DDR3 SDRAM、16MB QSPI Flash、PCIe Gen2 x8接口及丰富的扩展接口,支持高达1TeraMACs的DSP性能,其硬件设计采用8层PCB叠层,保证信号完整性,同时配备温度传感器和风扇散热系统,满足长时间稳定运行需求,开发板尺寸为220mm×180mm,符合工业标准机箱安装规范,适用于通信、工业控制、航空航天等领域。

核心模块详解

-

FPGA芯片

主芯片XC7K325T拥有325K逻辑单元、360个18×18 DSP48 slices、1040KB Block RAM,支持多达400个用户I/O,其676管脚封装提供丰富的高速接口,包括多个高速收发器(GTX/GTH),支持串行通信速率高达12.5Gbps。 -

存储系统

- DDR3内存:采用两颗512Mb DDR3 SDRAM(MT41K256M16),组成1GB 64位带宽存储,数据速率达1600Mbps,支持低功耗模式。

- Flash存储:16MB QSPI Flash(S25FL128SAGMF100)用于存储配置文件和用户程序,支持双路SPI模式,读取速度高达108Mbps。

- SD卡接口:兼容SDHC/SDXC卡,用于数据存储或系统启动。

-

时钟与电源管理

板载多路时钟源,包括100MHz差分晶振和多个可配置时钟缓冲器(MMCM),电源系统采用TI TPS65400等多相电源管理芯片,支持动态电压调节(DVR),满足FPGA内核、I/O及外围设备的供电需求,具备过流保护和温度监控功能。 (图片来源网络,侵删)

(图片来源网络,侵删)

接口资源分布

zc706提供丰富的外设接口,具体分布如下表所示:

| 接口类型 | 数量 | 关键特性 |

|---|---|---|

| PCIe Gen2 x8 | 1 | 支持×1/×4/×8模式,金手指连接器 |

| SATA 3.0 | 2 | 6Gbps速率,兼容SATA II/I标准 |

| USB 3.0 | 1 | Type-A接口,5Gbps带宽 |

| Gigabit Ethernet | 2 | RGMII接口,支持10/100/1000Mbps自适应 |

| UART | 2 | 3V/2.5V/1.8V可选电平,DB9连接器 |

| I2C/SPI | 各4路 | 支持多从机模式,兼容高速SPI(up to 50MHz) |

| GPIO | 64 | 3V兼容,部分支持LVDS电平 |

| FMC+ HPC | 1 | 400pin连接器,支持Zynq UltraScale+扩展 |

开发环境配置

-

软件工具

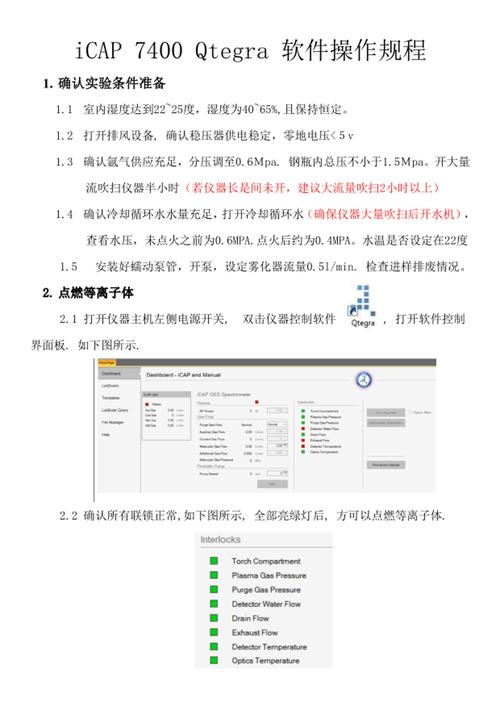

- Xilinx Vivado 2025.1或更高版本,支持原理图设计、HDL编码及综合。

- Linux操作系统(Ubuntu 18.04 LTS),推荐用于SDK开发。

- 必要的IP核:DDR3控制器(MIG PCIe硬核IP)。

-

开发流程

- 硬件设计:使用Vivado Block Design生成包含DDR3、PCIe等接口的顶层设计。

- 比特流生成:通过Implementation流程生成.bit文件,通过JTAG或QSPI Flash烧录。

- 软件开发:利用Vivado SDK或Petalinux开发嵌入式应用,支持C/C++及Python语言。

-

调试工具

板载JTAG USB接口(FT2232H芯片),支持Xilinx Cable调试;集成逻辑分析仪(ILA)和虚拟仪器(VIO),便于信号捕获与分析。

典型应用场景

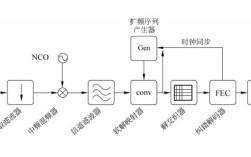

- 通信系统:利用FPGA实现5G基带处理、软件无线电(SDR)或高速数据包转发,结合PCIe接口与主机系统交互。

- 图像处理:通过DDR3缓存视频帧数据,利用DSP模块实现实时图像压缩或目标识别。

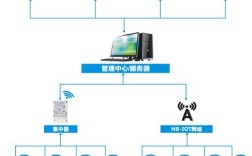

- 工业控制:通过GPIO和EtherCAT接口连接传感器与执行器,构建实时控制系统。

相关问答FAQs

Q1:zc706开发板支持哪些操作系统?

A1:zc706支持多种操作系统,包括裸机(Bare-metal)、实时操作系统(如VxWorks、FreeRTOS)以及Linux系统(通过Petalinux或Yocto Project构建),Linux系统需配合U-Boot引导程序,支持文件系统存储于eMMC或SD卡。

Q2:如何解决DDR3内存初始化失败的问题?

A2:DDR3初始化失败通常由以下原因导致:

(1)MIG IP核配置参数与硬件不匹配(如时序、Bank地址);

(2)PCB布局或电源噪声问题,需检查DDR3布线长度差是否控制在±50mil内;

(3)电压稳定性,使用示波器测量VTT电压是否为0.5×VDDQ,建议通过Vivado的Memory Interface Generator(MIG)工具生成符合硬件设计的约束文件,并执行硬件验证流程(HVL)。