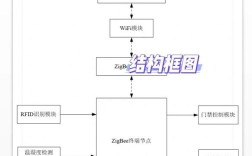

现代ASIC设计技术是当前集成电路产业的核心驱动力,随着摩尔定律的持续推进和应用场景的多元化,ASIC设计已经从传统的“设计-制造”二分模式发展为涵盖架构创新、工艺协同、智能化设计等多维度的复杂系统工程,其技术体系不仅关注性能、功耗和面积的平衡,更强调设计效率、可靠性和可扩展性,以满足人工智能、5G通信、物联网、自动驾驶等新兴领域对定制化芯片的迫切需求。

在架构设计层面,现代ASIC技术已从传统的通用计算转向领域专用架构(DSA),以AI芯片为例,设计者通过脉动阵列、稀疏化计算、量化压缩等技术,针对神经网络模型的计算特性定制数据流和硬件单元,显著提升能效比,NPU(神经网络处理器)通过集成张量核心、高带宽内存接口和专用指令集,将AI推理任务的功耗降低至通用CPU的1/10以下,异构计算架构成为主流,将CPU、GPU、DSP、FPGA等不同类型的计算单元通过高速互联总线(如CXL、UCIe)集成在单芯片中,兼顾灵活性与性能,在5G基站ASIC中,基带处理器通常集成大规模MIMO天线处理单元、信道编码模块和高速接口,通过动态电压频率调节(DVFS)技术实现不同负载下的能效优化。

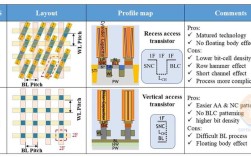

物理设计与工艺协同是现代ASIC技术的另一关键环节,随着制程节点进入7nm及以下,FinFET、GAA环绕栅晶体管等新型器件结构带来了设计复杂度的指数级增长,设计团队必须采用“设计-工艺协同优化”(DTCO)方法,在工艺开发阶段就介入电路设计,例如通过引入埋入电源轨(Power Rail)、多重曝光补偿等技术,解决先进工艺下的寄生参数、寄生效应和良率问题,在布局布线阶段,AI驱动的布局工具(如Google的Placement Cloud)通过强化学习算法优化单元放置,相比传统方法可提升10%-15%的布线效率,针对3D IC、芯粒(Chiplet)等先进封装技术,Die-to-Die互联设计成为重点,通过硅通孔(TSV)、混合键合等技术实现高带宽、低延迟的芯片间通信,例如AMD的Ryzen处理器采用Chiplet架构,将不同工艺节点的模块集成,在降低成本的同时提升性能。

验证与测试技术是保障ASIC功能可靠性的基石,现代ASIC设计规模已达百亿门级,传统基于仿真器的验证方法已无法满足效率需求,因此形式验证、硬件仿真加速(如FPGA原型验证)成为主流,形式验证通过数学方法证明设计逻辑的正确性,可快速覆盖状态空间,而硬件加速器将设计映射到FPGA板上,运行真实应用程序,发现仿真难以触及的时序和功耗问题,在测试阶段,内建自测试(BIST)技术被广泛应用,通过在芯片内部集成测试逻辑,实现存储器、高速接口等模块的自动测试,降低测试成本,针对AI芯片等新兴应用,在线测试(Built-in Self-Test, BIST)和机器学习辅助的故障诊断技术也逐渐兴起,通过实时监测芯片运行状态,定位异常模块并触发动态重构,提升系统容错能力。

设计方法学的智能化转型是现代ASIC技术的显著特征,基于云的协同设计平台(如Cadence Cloud Engine)支持全球多团队实时协作,通过版本控制和设计数据管理(PLM)系统确保设计一致性,AI技术深度渗透设计全流程:在逻辑综合阶段,机器学习模型根据设计参数预测时序和功耗,指导综合工具优化;在物理设计阶段,图神经网络(GNN)用于预测布线拥塞,减少迭代次数;在测试阶段,强化学习算法生成最优测试向量,提升故障覆盖率,低代码/无代码设计平台(如Siemens的Mentor Graphics)通过IP复用和可视化编程,降低ASIC设计的门槛,使系统工程师也能参与芯片设计,加速产品上市。

现代ASIC设计仍面临诸多挑战,首先是成本问题,7nm及以下工艺的研发和制造成本已超过20亿美元,中小型企业难以承担,因此芯粒架构、开源指令集(如RISC-V)和设计服务外包成为降低成本的有效途径,其次是设计周期与市场需求的矛盾,复杂ASIC的设计周期通常长达18-24个月,而消费电子产品的更新周期仅12-18个月,这要求采用模块化设计和敏捷开发方法,通过预验证IP库快速构建芯片,安全性和可靠性问题日益突出,侧信道攻击、硬件木马等威胁对芯片安全构成挑战,设计时需集成物理不可克隆函数(PUF)、加密引擎等安全模块,并通过形式化验证确保其正确性。

相关问答FAQs

Q1:现代ASIC设计与传统FPGA设计相比有哪些核心优势?

A1:现代ASIC设计在性能、功耗、成本和集成度上具有显著优势,ASIC针对特定应用深度优化,可实现比FPGA高3-5倍的运算性能,功耗降低50%以上,且大规模生产后单片成本远低于FPGA,ASIC支持更先进的工艺节点(如3nm、2nm)和更复杂的集成度(如百亿晶体管),适合对功耗、面积和成本(PPA)要求严苛的场景,如高端服务器、AI训练芯片等,而FPGA的优势在于灵活性,适合原型验证、小批量生产或需要频繁迭代的应用,但其架构限制导致性能和能效无法与定制ASIC相比。

Q2:芯粒(Chiplet)技术如何解决现代ASIC设计的成本和良率问题?

A2:芯粒技术通过将复杂ASIC拆分为多个采用不同工艺节点的独立芯片(芯粒),再通过先进封装(如2.5D/3D封装)集成,有效降低成本和风险,芯粒允许采用成熟工艺(如28nm)实现非关键模块,仅对计算密集型模块使用先进工艺(如5nm),大幅减少先进工艺的芯片面积和制造成本;小尺寸芯粒的良率显著高于单芯片大尺寸裸片,即使某个芯粒失效,仅需替换对应模块而非整个芯片,提升整体良率,Intel的Foveros技术通过堆叠芯粒,实现了计算、存储、I/O模块的高密度集成,在降低成本的同时满足高性能需求。