EDA技术作为现代电子设计领域的核心工具,通过计算机辅助设计实现了电子系统从概念到实现的全流程自动化,在数字逻辑设计中,分频计数作为基础且关键的模块,其实现效率直接影响系统性能,EDA工具通过硬件描述语言(HDL)如Verilog或VHDL的编写与仿真,结合综合、布局布线等流程,显著提升了分频计数电路的设计精度与开发效率,分频计数电路的核心功能是对输入时钟信号进行频率分频或周期计数,常见的包括偶数分频、奇数分频及小数分频等类型,一个N分频计数器通过N进制计数逻辑,每N个时钟周期输出一个脉冲,从而将输入时钟频率降低为原来的1/N,EDA技术在此过程中的优势体现在多方面:在行为级建模阶段,设计者可通过HDL描述分频计数器的功能逻辑,如使用always块实现计数状态机,EDA工具通过仿真验证逻辑正确性,避免传统原理图设计的繁琐与错误;在逻辑综合阶段,EDA工具将HDL代码转换为门级网表,并针对目标器件(如FPGA或ASIC)进行优化,如选择合适的触发器类型、减少逻辑资源占用,对于分频计数器中常见的模值控制,综合工具会自动生成高效的译码电路;在物理实现阶段,布局布线工具考虑时钟 skew、延迟等约束,确保分频输出信号的时序满足系统要求,尤其是对于高频分频场景,时序分析功能可有效防止亚稳态问题。

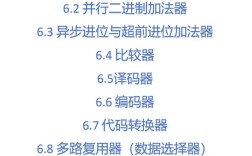

分频计数电路的设计需结合具体应用场景选择合适结构,以偶数分频为例,一个4分频计数器可通过2位二进制计数器实现,计数状态从00递增到11,当计数达到最大值时复位,同时将最高位作为分频输出,对于奇数分频,如3分频,通常采用脉冲吞咽技术或状态机设计,通过控制计数器的复位条件实现不对称的占空比输出,EDA工具提供的参数化设计方法简化了此类过程,例如通过定义分频参数N,生成可配置的通用分频模块,支持不同分频需求的快速复用,在复杂系统中,往往需要多级分频级联,如先进行8分频再进行2分频实现16分频,EDA工具的层次化设计能力允许将各级分频模块封装为子模块,通过顶层模块调用,既保证了设计的模块化,又便于调试与维护,对于小数分频需求(如2.5分频),可通过脉冲插入技术实现,EDA工具的状态机优化功能可确保脉冲分布的均匀性,减少输出信号的相位抖动。

从实现资源的角度看,分频计数器的资源消耗与分频模值、计数器位宽直接相关,以FPGA实现为例,一个N位二进制计数器需要N个触发器及相应的组合逻辑资源,EDA工具在综合过程中会进行资源评估,并通过优化算法(如状态编码优化、逻辑共享)降低资源占用,对于模值较大的分频器(如100分频),采用十进制BCD码计数而非二进制计数,可减少译码逻辑的复杂度,综合工具会自动根据目标器件的架构选择最优实现方式,EDA时序分析工具可生成详细的时序报告,包括建立时间(Setup Time)、保持时间(Hold Time)及时钟到输出延迟(Clock-to-Output Delay),帮助设计者识别并解决时序违规问题,这对于高速分频电路尤为重要,例如在通信系统中,分频时钟的精度直接影响数据采样的准确性。

随着EDA技术的发展,高级综合(HLS)工具允许使用C/C++等高级语言描述分频计数算法,自动生成优化的HDL代码,进一步缩短了设计周期,基于机器学习的优化算法可分析历史设计数据,为分频计数器的结构选择提供建议,如针对特定应用场景推荐最优的分频实现方案,在SoC设计中,分频计数器常作为时钟管理模块的一部分,与PLL(锁相环)配合使用,实现多频率时钟域的生成与管理,EDA工具的全流程支持确保了时钟网络的低 skew与低功耗设计。

相关问答FAQs

-

问:EDA技术中如何实现占空比为50%的奇数分频器?

答: 实现占空比50%的奇数分频器(如3分频)可采用双计数器法或状态机控制法,以3分为例,设计一个2位计数器,状态循环为00→01→10→00,当计数到01时输出高电平,计数到10时输出低电平,通过控制输出信号的翻转时刻,使高电平持续1.5个时钟周期,低电平持续1.5个时钟周期,从而实现50%占空比,EDA工具可通过Verilog的always块结合条件判断语句实现该逻辑,综合工具会自动优化生成满足时序要求的门级电路。 -

问:在FPGA设计中,使用EDA工具进行分频计数器综合时,如何优化资源占用?

答: 优化资源占用可从以下方面入手:①选择合适的计数器类型,如模值较小时采用格雷码计数减少译码逻辑;②利用EDA工具的参数化设计,通过共享子模块减少重复逻辑;③使用触发器链(LUT触发器)资源,对于简单分频器直接使用查找表实现计数逻辑;④进行状态编码优化,如one-hot编码适用于状态较少的情况,二进制编码适用于状态较多的情况;⑤启用综合工具的面积优化选项,如Xilinx的XST或Intel的Quartus Prime中的"Area Optimization"模式,工具会自动平衡资源与时序需求。