FPGA(现场可编程门阵列)与EDA(电子设计自动化)技术是现代电子设计领域中相辅相成的核心组成部分,EDA技术为FPGA的设计、开发、验证和实现提供了全流程的工具支持,而FPGA凭借其可重构、高并行、低延迟的特性,在通信、工业控制、人工智能、航空航天等领域得到了广泛应用,两者的结合不仅推动了电子设计方法的革新,也加速了技术创新的进程。

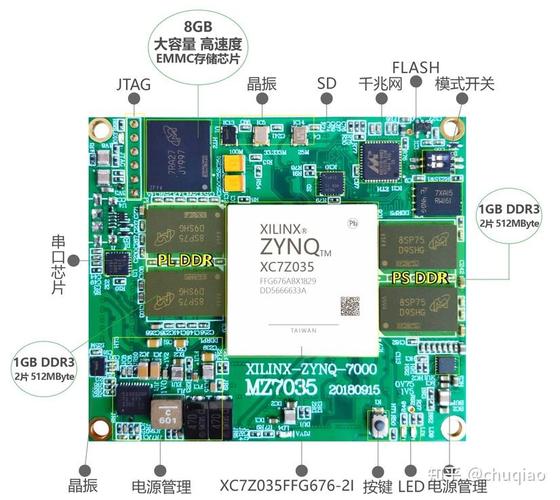

FPGA是一种半定制化的集成电路,通过内部的可编程逻辑单元、输入输出单元和布线资源,用户可以根据需求配置硬件电路,实现特定的功能,与ASIC(专用集成电路)相比,FPGA的开发周期短、设计灵活性高,适合快速原型验证和小批量生产,FPGA的设计复杂度较高,需要借助EDA工具完成从逻辑设计到物理实现的完整流程,EDA技术则以计算机辅助设计为基础,涵盖了硬件描述语言(HDL)编写、逻辑综合、仿真验证、布局布线、时序分析等多个环节,是确保FPGA设计正确性和高效性的关键。

在FPGA设计的初始阶段,EDA工具提供了高层次的建模与仿真环境,工程师可以使用Verilog、VHDL等硬件描述语言,或SystemC、High-Level Synthesis(HLS)等高层次设计方法,对系统功能进行描述,EDA仿真工具(如ModelSim、Xilinx Vivado Simulator)通过行为级、RTL级(寄存器传输级)和门级仿真,验证设计的逻辑功能是否正确,这一阶段的重点是发现功能错误,避免后续设计返工,在通信系统中,工程师可以通过仿真验证调制解调算法的正确性,确保数据传输的准确性。

逻辑综合是将RTL代码转换为逻辑门网表的过程,依赖EDA综合工具(如Synopsys Design Compiler、Xilinx Vivado)的优化算法,工具会根据FPGA的架构特性,对逻辑进行化简、映射和优化,生成与目标器件兼容的门级网表,这一阶段需要兼顾资源利用率和性能,例如通过资源共享减少逻辑单元数量,或通过流水线技术提高系统吞吐量,对于大规模FPGA设计,综合阶段的优化直接影响后续布局布线的效率和最终时序。

布局布线是FPGA设计中最耗时的环节之一,EDA工具通过自动或交互式的方式,将逻辑网表映射到FPGA的物理资源上,布局工具确定逻辑单元在芯片中的位置,布线工具则完成单元间的连线,由于FPGA的布线资源有限,布局布线的质量直接影响时序性能,现代EDA工具采用智能算法(如模拟退火、遗传算法)优化布局,避免拥塞;通过时序驱动的布线(Timing-Driven Placement and Routing)满足关键路径的时序约束,在高速图像处理应用中,布局布线工具需确保像素数据通路的时序裕量满足实时处理要求。

时序分析是确保FPGA设计满足频率要求的关键步骤,EDA工具通过静态时序分析(STA)计算信号在路径上的传播延迟,检查建立时间(Setup Time)和保持时间(Hold Time)是否 violated,与时序仿真相比,STA无需遍历所有输入向量,效率更高,适合大规模设计,对于不满足时序约束的路径,EDA工具提供时序报告和优化建议,如调整布局、插入寄存器或重新综合,在5G基站中,FPGA的基带处理单元需要满足严格的时序要求,以确保信号同步和低误码率。

除了传统的设计流程,EDA技术还推动了FPGA的高层次设计(HLS)和异构集成的发展,HLS工具(如Xilinx Vitis HLS、Intel HLS)允许工程师使用C/C++或Python描述算法,自动生成RTL代码,缩短了软件工程师向硬件设计的转型周期,EDA工具支持FPGA与CPU、GPU等处理器的异构协同设计,通过统一编程模型(如OpenCL)优化任务分配,在自动驾驶领域,FPGA通过HLS快速实现传感器融合算法,与CPU协同处理实时决策任务。

FPGA与EDA技术的结合也面临挑战,随着工艺节点的进步,FPGA的规模和复杂度呈指数级增长,对EDA工具的算法和性能提出了更高要求,7nm及以下工艺的FPGA设计需要考虑功耗、热效应和信号完整性等问题,EDA工具需引入更精确的建模和分析方法,AI技术的融入正在改变EDA工具的设计模式,机器学习算法被用于优化布局布线、预测时序违例,进一步提高设计效率。

以下通过表格对比FPGA设计各阶段EDA工具的主要功能:

| 设计阶段 | EDA工具示例 | 主要功能 |

|---|---|---|

| 功能仿真 | ModelSim、QuestaSim | 行为级、RTL级仿真,验证设计逻辑正确性 |

| 逻辑综合 | Synopsys DC、Vivado Synthesis | 将RTL代码转换为门级网表,优化逻辑资源 |

| 布局布线 | Vivado、Quartus Prime | 将网表映射到FPGA物理资源,完成单元布局和连线 |

| 时序分析 | TimeQuest、PrimeTime | 静态时序分析,检查时序约束,优化关键路径 |

| 高层次设计 | Vitis HLS、Intel HLS | C/C++/Python转RTL,加速算法硬件化 |

| 物理验证 | Calibre、IC Validator | DRC(设计规则检查)、LVS(版图对比验证)确保物理实现正确性 |

相关问答FAQs:

-

问:FPGA设计为什么必须依赖EDA工具?

答:FPGA设计涉及复杂的逻辑功能实现、资源优化和时序约束,手动完成这些任务几乎不可能,EDA工具提供了从仿真、综合到布局布线的全流程支持,能够自动化优化设计、发现潜在错误,并确保最终电路满足性能和可靠性要求,EDA工具的时序分析功能可以避免因信号延迟导致的系统故障,而布局布线工具则能高效利用FPGA的有限资源。 -

问:HLS技术如何改变FPGA的设计流程?

答:HLS(高层次设计)技术允许工程师使用高级语言(如C/C++)描述算法,通过EDA工具自动生成RTL代码,大幅降低了硬件设计的门槛,传统FPGA设计需要工程师精通硬件描述语言和底层架构,而HLS使软件工程师能够快速实现硬件加速,缩短了开发周期,在AI推理任务中,HLS可将神经网络模型直接转换为FPGA硬件电路,无需手动编写复杂的逻辑代码。