VHDL可逆计数器是一种基于可逆逻辑设计的数字电路,能够在不丢失信息的前提下实现计数操作,与传统不可逆计数器相比具有能耗低、信息无损等优势,在量子计算、低功耗设计等领域具有重要应用价值,可逆逻辑的核心思想是确保每个输入和输出组合一一对应,避免信息熵增,从而减少计算过程中的能量损耗,在VHDL中实现可逆计数器需要严格遵循可逆逻辑规则,通过设计特定的门电路结构来实现计数功能。

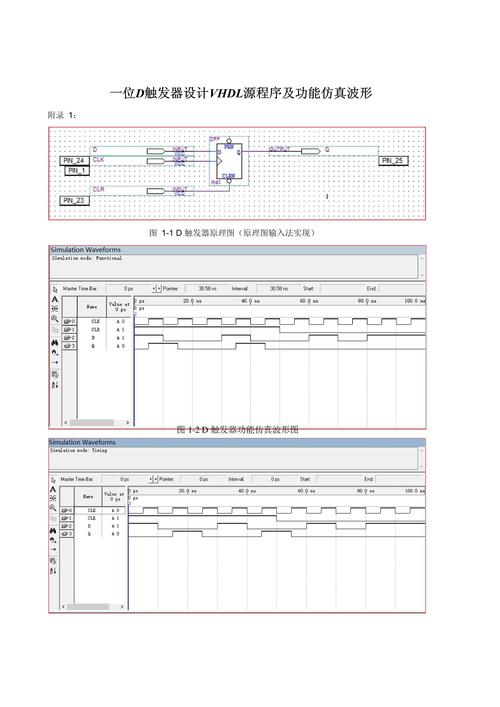

可逆计数器的基本结构通常由可逆逻辑门组成,如Toffoli门、Fredkin门等,这些门电路能够实现可逆的逻辑运算,以3位可逆计数器为例,其需要处理8种状态转换,每个状态变化都需确保输入和输出的可逆性,在VHDL代码设计中,首先需要定义计数器的实体和架构,实体部分明确输入输出端口,架构部分描述逻辑功能,输入信号包括时钟信号clk、复位信号rst,输出信号为3位计数状态count,同时可能需要设置可逆操作的控制信号。

在具体实现过程中,可采用模块化设计方法,将可逆计数器分解为状态生成模块和逻辑控制模块,状态生成模块负责根据时钟信号产生计数状态,逻辑控制模块则通过可逆逻辑门实现状态转换,VHDL描述中,进程语句(process)常用于描述时序逻辑,通过敏感信号(如clk和rst)的变化触发状态更新,在复位信号有效时,计数器清零;在时钟上升沿时,计数器按照可逆逻辑规则递增或递减,为了确保可逆性,状态转换过程中需要避免信息丢失,这意味着每个状态必须有唯一的对应输入,且状态转换函数必须是一一映射的。

可逆计数器的优势在于其低功耗特性,传统计数器在状态变化时会产生瞬态功耗,而可逆计数器由于信息无损,理论上能够接近Landauer极限(每比特操作能耗约kTln2),可逆计数器在量子计算中具有重要应用,因为量子操作本质上是可逆的,可逆计数器可以作为量子算法的基本构建模块,可逆计数器的设计也面临挑战,如逻辑门结构复杂、硬件资源消耗较大等,因此在实际应用中需要权衡性能与资源开销。

以下是一个简化的3位可逆计数器VHDL代码框架示例:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity reversible_counter is

Port (clk : in STD_LOGIC;

rst : in STD_LOGIC;

count : out STD_LOGIC_VECTOR(2 downto 0));

end reversible_counter;

architecture Behavioral of reversible_counter is

signal count_reg : STD_LOGIC_VECTOR(2 downto 0);

begin

process(clk, rst)

begin

if rst = '1' then

count_reg <= "000";

elsif rising_edge(clk) then

-- 可逆逻辑状态转换示例

count_reg <= std_logic_vector(unsigned(count_reg) + 1);

end if;

end process;

count <= count_reg;

end Behavioral;

需要注意的是,上述代码中的状态转换部分需要进一步优化以严格满足可逆逻辑要求,例如通过自定义可逆逻辑门实现加法操作。

为了更清晰地展示可逆计数器的状态转换特性,以下表格列举了3位可逆计数器的部分状态转换关系(假设为递增计数):

| 当前状态 (输入) | 控制信号 | 下一状态 (输出) | 可逆性验证 |

|---|---|---|---|

| 000 | 0 | 001 | 输出唯一 |

| 001 | 0 | 010 | 输出唯一 |

| 010 | 0 | 011 | 输出唯一 |

| 011 | 0 | 100 | 输出唯一 |

| 100 | 0 | 101 | 输出唯一 |

| 101 | 0 | 110 | 输出唯一 |

| 110 | 0 | 111 | 输出唯一 |

| 111 | 0 | 000 | 输出唯一 |

表格中的控制信号用于选择计数方向(递增/递减),可逆性验证确保每个输出状态仅对应一个输入状态,在实际设计中,可能需要引入额外的辅助信号来实现严格的可逆映射,这会增加电路的复杂度。

相关问答FAQs:

-

问:可逆计数器与传统计数器的主要区别是什么?

答:可逆计数器遵循可逆逻辑原则,确保每个输入和输出状态一一对应,避免信息丢失,从而降低能耗;而传统计数器在状态转换时可能产生信息熵增,导致较高的瞬态功耗,可逆计数器的逻辑设计更复杂,通常需要特殊的可逆逻辑门(如Toffoli门)实现,而传统计数器可采用简单的触发器和组合逻辑设计。 -

问:在VHDL中实现可逆计数器时需要注意哪些关键点?

答:首先需严格遵循可逆逻辑规则,确保状态转换函数是一一映射;合理设计控制逻辑,避免信息丢失;需优化代码结构,平衡硬件资源消耗与性能;需通过仿真验证可逆性,确保所有状态转换均满足输入输出唯一对应关系,实际设计中可能需要引入辅助信号或自定义可逆逻辑门来实现复杂功能。