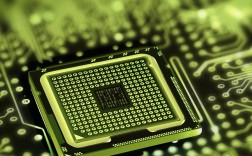

纳米技术是微电子技术的关键驱动力,二者在发展路径、技术原理和应用层面深度交织,共同推动了信息时代的进步,微电子技术以集成电路为核心,通过不断缩小器件尺寸来提升集成度和运算速度,而纳米技术则为这种“微型化”提供了底层支撑,使其突破物理极限,迈向更深层次的尺度变革。

从技术本质看,微电子技术的核心是利用半导体材料(如硅)制造晶体管等元器件,通过光刻、刻蚀等工艺在芯片上形成微观电路,当器件尺寸进入纳米尺度(通常指100纳米以下),传统微电子工艺面临量子效应、散热、功耗等挑战,而纳米技术通过原子级操控、材料改性和新结构设计,为这些问题提供了解决方案,纳米薄膜技术可提升晶体管的栅极控制能力,减少漏电流;纳米线、纳米管等新型材料则替代传统硅材料,成为突破摩尔定律限制的候选方案;而自组装纳米技术能实现更精细的电路图案,提升光刻精度。

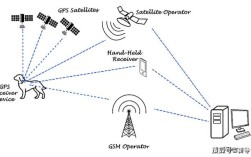

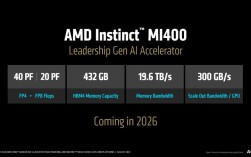

在应用层面,纳米技术与微电子技术的融合催生了众多颠覆性创新,在计算领域,基于纳米技术的FinFET(鳍式场效应晶体管)结构已成为先进制程的主流,通过三维设计解决了短沟道效应,使芯片性能持续提升;在存储领域,纳米点存储技术、阻变存储器等利用纳米尺度材料的特性,实现了更高密度、更快速度的数据存储;在通信领域,纳米材料(如石墨烯)被用于制造高频、低功耗的射频器件,推动5G/6G技术的发展,纳米电子学与生物技术的结合,还催生了纳米传感器、生物芯片等新型器件,为医疗诊断、环境监测等领域提供精准工具。

二者的协同发展也离不开制造工艺的进步,传统光刻技术受限于光的衍射极限,难以实现10纳米以下的精细加工,而纳米技术引入的极紫外光刻(EUV)、电子束光刻、纳米压印等技术,通过更短的波长或物理接触方式,实现了原子级精度的图案化,EUV光刻使用13.5纳米波长的极紫外光,结合多重曝光技术,已支持3纳米及以下制程的量产,这本质上是纳米技术对微电子制造工艺的深度赋能。

纳米技术赋能微电子技术的同时,也带来了新的挑战,纳米尺度的器件对制造环境的洁净度、材料纯度要求极高,导致生产成本指数级上升;量子隧穿效应、热载流子注入等纳米尺度下的物理现象,也增加了电路设计的复杂性,纳米材料的稳定性、可靠性以及大规模量产的一致性,仍是需要攻克的难题,这些问题促使研究者探索新的技术路径,如三维集成、异质集成、量子计算等,而纳米技术将继续在这些领域发挥核心作用。

相关问答FAQs

Q1:纳米技术如何帮助微电子技术突破摩尔定律的限制?

A1:摩尔定律指出集成电路上的晶体管数量每18-24个月翻一番,但随着器件尺寸接近物理极限(如5纳米以下),传统平面晶体管面临短沟道效应、漏电流剧增等问题,纳米技术通过多种方式突破这一限制:一是采用三维结构(如FinFET、GAA环绕栅晶体管),通过增加栅极与沟道的接触面积,增强电场控制能力;二是引入新型纳米材料(如碳纳米管、石墨烯),其优异的电学特性可替代硅材料,实现更高速度和更低功耗;三是利用纳米自组装、定向自组装等技术,实现更精细的电路图案,提升集成密度,纳米级封装和三维堆叠技术也能在不缩小单器件尺寸的情况下,通过垂直集成增加芯片功能密度,延续摩尔定律的发展。

Q2:纳米技术在微电子制造中的主要挑战有哪些?

A2:纳米技术在微电子制造中面临三大核心挑战:一是工艺精度与成本挑战,当制程进入7纳米以下,极紫外光刻(EUV)等设备成本高昂(单台超过1.5亿美元),且对环境振动、温度控制要求极严,导致量产成本大幅上升;二是物理效应挑战,纳米尺度下量子隧穿、量子涨落等效应显著,可能引发器件漏电、性能不稳定,传统电路设计模型失效;三是材料与可靠性挑战,纳米材料(如二维材料)的表面活性高,易受环境杂质影响,导致器件寿命缩短,同时纳米尺度缺陷的检测与修复难度极大,这些挑战促使行业探索新工艺(如定向自组装光刻)和新材料(如二维半导体),以实现纳米级制造的可靠性与经济性平衡。