FinFET技术作为半导体制造领域的一项革命性突破,其核心特点在于通过三维结构设计解决了传统平面晶体管的短沟道效应问题,为先进制程节点的性能提升与功耗控制奠定了基础,从技术原理到应用优势,FinFET的多维度特性使其成为当前主流芯片制造的关键技术。

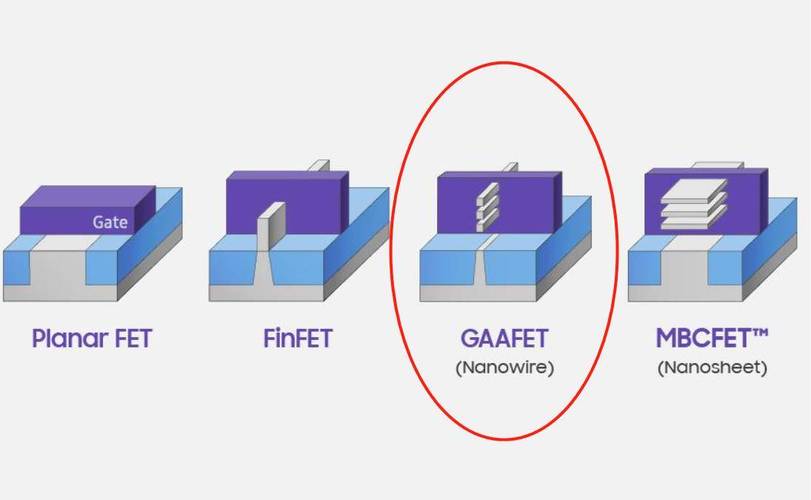

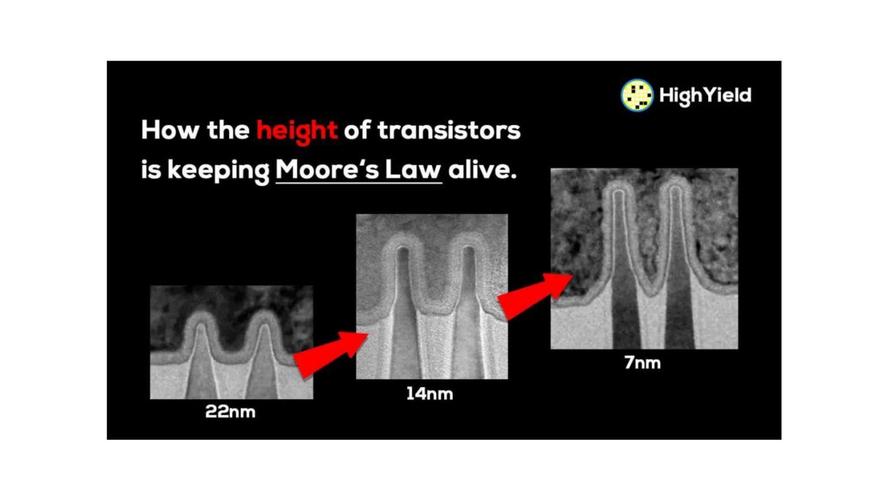

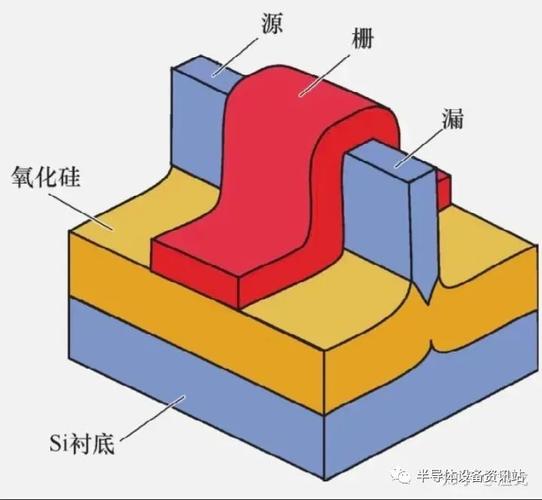

FinFET的全称为“场效应晶体管”,其最显著的结构创新在于将传统的二维平面沟道转变为三维“鳍”状结构,在传统平面晶体管中,栅极仅从顶部覆盖沟道,随着制程工艺不断缩小(如从28nm迈向7nm、5nm甚至更先进节点),沟道长度缩短导致栅极对沟道的控制能力减弱,电子容易从源极直接“泄漏”到漏极,即短沟道效应,进而引发漏电流增加、功耗上升和性能不稳定等问题,FinFET通过在沟道两侧增加垂直栅极,形成类似鱼鳍的三维结构,使栅极从三个方向(顶部、左侧、右侧)包裹沟道,显著增强了栅极对沟道的静电控制能力,这种三维设计有效抑制了短沟道效应,使得晶体管在更小的尺寸下仍能保持稳定的开关特性,为制程微缩提供了可能。

在性能提升方面,FinFET技术展现出多维度优势,驱动电流得到显著增强,由于栅极对沟道的覆盖面积增加,沟道中的载流子(电子或空穴)运动更易受栅极电场控制,从而提高了电流通过效率,在16nm/14nm节点,FinFET的驱动电流相比传统平面晶体管可提升30%-50%,这意味着芯片的运行速度更快,数据处理能力更强,开关性能优化明显,三维栅极结构使得晶体管的阈值电压(开启沟道所需的最低电压)更稳定,亚阈值摆幅(衡量开关陡峭程度的指标)更接近理论极限(约60mV/decade),减少了漏电流,降低了静态功耗,这对于移动设备等对功耗敏感的场景尤为重要,可显著延长电池续航时间,FinFET还具备更好的工艺兼容性,在现有制造设备基础上,通过调整光刻、刻蚀等工艺步骤即可实现FinFET结构的构建,无需彻底颠覆现有产线,降低了先进制程的研发与生产成本。

功耗控制是FinFET的另一核心优势,传统平面晶体管在微缩过程中,漏电流会随沟道长度缩短呈指数级增长,导致静态功耗(芯片待机时的功耗)急剧上升,成为限制芯片集成度的主要瓶颈,FinFET的三维栅极结构通过增强沟道控制,将漏电流降低了1-2个数量级,使得芯片在高集成度下仍能保持较低的静态功耗,在智能手机SoC中,采用FinFET技术的芯片相比同制程平面晶体管芯片,静态功耗可降低40%-60%,有效解决了设备发热问题,动态功耗(芯片工作时的功耗)也因驱动电流的优化得到改善——在相同性能要求下,FinFET可降低工作电压,进一步减少动态功耗损耗,这种“高能效比”特性使FinFET成为移动计算、数据中心、人工智能等领域的理想选择。

可靠性提升是FinFET技术的隐形优势,短沟道效应不仅影响功耗和性能,还会加剧热载流子注入(HCI)和负偏温不稳定性(NBTI)等效应,导致晶体管长期使用后性能退化,FinFET的三维结构通过减少漏电流和电场集中现象,降低了热载流子对栅介质的损伤,提升了器件的长期稳定性,实验数据显示,在相同工作条件下,FinFET的寿命相比平面晶体管可延长2-3倍,这对于需要长期稳定运行的服务器芯片、汽车电子芯片等高可靠性场景至关重要。

从制造工艺角度看,FinFET的结构复杂性也带来了新的挑战,FinFET的“鳍”结构需要通过高深宽比刻蚀技术形成,对刻蚀均匀性、侧壁粗糙度控制要求极高;栅极与沟道的环绕结构也使得原子层沉积(ALD)等工艺的难度增加,需精确控制栅介质厚度与功函数金属的沉积均匀性,随着制程进一步微缩(如5nm以下),FinFET的“鳍”宽需缩小至几纳米,量子隧穿效应可能再次成为限制因素,这也是行业正在探索纳米片(GAA)等更先进结构的原因,尽管如此,FinFET凭借其成熟的技术积累和综合优势,在7nm、5nm等节点仍占据主导地位,预计在未来3-5年内仍将是先进芯片制造的核心技术。

以下为FinFET技术关键特点的对比总结:

| 特性维度 | 传统平面晶体管 | FinFET技术 | 优势体现 |

|---|---|---|---|

| 沟道结构 | 二维平面结构 | 三维“鳍”状结构,栅极三面包裹 | 增强栅极控制,抑制短沟道效应 |

| 静电控制能力 | 栅极仅覆盖沟道顶部,控制较弱 | 栅极覆盖沟道三侧,控制能力强 | 降低漏电流,提高开关性能 |

| 驱动电流 | 受限于沟道长度,微缩后下降明显 | 三维结构增大沟道宽度,电流提升30%-50% | 提升芯片运行速度 |

| 功耗表现 | 静态功耗随微缩指数级增长 | 静态功耗降低40%-60%,动态功耗优化 | 延长续航,减少发热 |

| 可靠性 | 热载流子效应明显,性能易退化 | 漏电流降低,器件寿命延长2-3倍 | 适用于高可靠性场景 |

| 工艺兼容性 | 微缩至10nm以下后瓶颈显著 | 基于现有设备调整,成本可控 | 降低先进制程研发与生产难度 |

相关问答FAQs

Q1:FinFET相比传统平面晶体管,为什么能更好地控制功耗?

A1:FinFET通过三维“鳍”状结构使栅极从三个方向包裹沟道,显著增强了栅极对沟道的静电控制能力,有效抑制了短沟道效应,这种结构大幅降低了漏电流(静态功耗的主要来源),同时允许在相同性能下降低工作电压(减少动态功耗),在14nm节点,FinFET的漏电流可比平面晶体管降低1-2个数量级,静态功耗减少40%-60%,从而实现整体功耗的优化。

Q2:FinFET技术在制造过程中面临的主要挑战有哪些?

A2:FinFET的制造挑战主要体现在结构复杂性和工艺精度上:“鳍”结构需通过高深宽比刻蚀技术形成,对刻蚀均匀性、侧壁粗糙度控制要求极高;栅极与沟道的环绕结构使得原子层沉积(ALD)等工艺难度增加,需精确控制栅介质厚度与金属沉积均匀性;随着制程进一步微缩(如5nm以下),“鳍”宽缩小至纳米级时,量子隧穿效应可能成为新的瓶颈,对设备精度和材料提出更高要求。