DDR内存中的ODT(On-Die Termination)技术是提升信号完整性、确保高速数据传输可靠性的关键设计,尤其在现代高性能计算和数据中心领域发挥着不可替代的作用,要深入理解ODT技术,需从信号传输的基本问题入手,分析其工作原理、实现方式及在不同场景下的应用逻辑。

在高速数字电路中,信号沿传输线传播时若遇到阻抗不匹配,会发生反射现象,导致信号畸变、眼图闭合,甚至引发数据误判,传统解决方案是在主板设计外置终端电阻,但这种方式存在明显局限:电阻参数需根据实际走线长度、拓扑结构精确匹配,调试复杂;终端电阻会持续消耗功率,且在多负载场景下难以兼顾不同分支的阻抗匹配,DDR内存作为高频工作的核心部件,数据传输速率从DDR2时代的数百Mbps提升至DDR5的数Gbps,信号反射问题愈发突出,ODT技术因此应运而生。

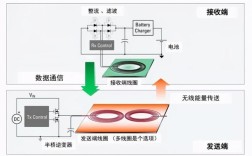

ODT技术的核心在于将终端电阻直接集成到内存芯片内部,通过控制器动态配置电阻值,实现阻抗的实时匹配,其工作原理可概括为:当内存控制器(MCU)向内存颗粒发送数据(写操作)或接收数据(读操作)时,会通过控制信号(如DDR4中的MODT寄存器)启用或禁用ODT功能,并设置对应的终端电阻阻值,在写操作中,MCU作为驱动端,会启用ODT功能,使内存颗粒内部的终端电阻与传输线阻抗匹配,吸收信号能量,防止反射;在读操作中,MCU作为接收端,则需关闭自身端的ODT(若支持),避免与内存颗粒的ODT形成并联,破坏阻抗匹配,这种动态切换机制既解决了信号反射问题,又避免了终端电阻的持续功耗浪费。

从技术演进看,ODT支持能力随DDR代际升级不断完善,在DDR2时代,ODT首次被引入,仅支持内存颗粒端的终端配置,且阻值固定(通常为50Ω或75Ω),控制器端仍需外置终端电阻,到了DDR3,ODT功能扩展至控制器端,支持动态调整阻值(如40Ω、60Ω、120Ω等),以适应不同负载和走线拓扑;内存颗粒端的ODT阻值也变为可配置,进一步提升了灵活性,DDR4在此基础上增加了per-bit ODT(每比特终端)功能,允许对DQ、DM、DQS等信号线分别设置终端电阻,解决了高速信号中不同信号线阻抗差异问题,而DDR5则进一步优化了ODT的 granularity(粒度),支持更精细的阻值调整(如30Ω至120Ω范围内多档可选),并新增了ODT Calibration(校准)机制,通过硬件自动检测阻抗匹配状态,减少人工干预。

ODT技术的应用场景需根据信号传输方向严格区分,以DDR4为例,在写操作(MCU→DRAM)时,MCU会通过CS#(片选)信号和地址/命令线上的ODT控制位,通知目标内存颗粒启用内部终端电阻,阻值由MODT寄存器预设(如60Ω);MCU端的ODT应保持禁用,避免与DRAM端的ODT形成并联,导致等效阻抗过低,在读操作(DRAM→MCU)时,则相反:DRAM颗粒关闭ODT,MCU启用自身端的ODT(通常为40Ω或50Ω),以接收来自内存的信号,这种“写操作终端在DRAM、读操作终端在MCU”的对称设计,确保了信号在驱动端和接收端都能实现阻抗匹配,值得注意的是,在多DIMM(内存条)并行系统中,未选中的DIMM需禁用ODT,避免对正在通信的信号线产生并联影响,这通过DIMM的片选信号和寄存器配置实现。

ODT技术的优势显著,但也存在设计挑战,其核心优势在于:1)提升信号完整性:消除反射,改善眼图高度和抖动,支持更高频率;2)简化主板设计:减少外置终端电阻数量,降低布线复杂度和成本;3)动态功耗优化:仅在需要时启用ODT,避免空闲时的静态功耗,ODT的配置需综合考虑信号拓扑(如T型拓扑、Fly-by拓扑)、负载数量、走线长度等因素,错误的阻值选择可能导致信号过阻尼或欠阻尼,反而加剧反射,ODT的切换时间(从禁用到启用或反之)需小于信号周期,避免在数据传输过程中产生阻抗突变,这对内存控制器和颗粒的时序设计提出了更高要求。

为更直观展示不同DDR代际ODT技术的差异,可参考下表:

| 特性 | DDR2 | DDR3 | DDR4 | DDR5 |

|---|---|---|---|---|

| ODT支持位置 | 仅DRAM端 | DRAM端+控制器端 | DRAM端+控制器端 | DRAM端+控制器端 |

| 阻值可调性 | 固定(50/75Ω) | 多档可调(40/60/120Ω) | 多档可调(40/60/120Ω等) | 高精度可调(30-120Ω多档) |

| per-bit ODT | 不支持 | 不支持 | 支持(DQ/DM/DQS分别配置) | 支持,且支持更细分配置 |

| 校准机制 | 无 | 无 | 手动配置 | 自动硬件校准 |

| 典型应用场景 | 低端服务器 | 消费级/企业级 | 高性能计算/数据中心 | AI服务器/高端工作站 |

在实际应用中,ODT参数的配置需结合内存控制器的初始化代码和内存颗粒的规格书,DDR4 SODIMM(笔记本内存条)通常采用2-rank(双rank)设计,在写操作时,控制器需根据当前激活的rank动态调整ODT阻值,若两个rank同时被访问,可能需启用并联ODT配置(等效阻值降低),ODT的上升/下降时间(RT/FT)参数也需优化,过快的切换速度可能产生高频噪声,过慢则影响信号建立时间,这需要通过示波器等工具进行信号质量调试。

相关问答FAQs:

Q1:ODT技术是否会增加内存芯片的功耗?

A1:是的,但功耗影响可控,ODT终端电阻仅在启用时消耗功率,且阻值较高(通常40Ω以上),静态电流较小,相比外置终端电阻的持续功耗,ODT的动态启用机制反而降低了整体功耗,DDR4内存颗粒在启用ODT时,额外功耗约增加5%-10%,但通过关闭空闲rank的ODT,可进一步优化功耗。

Q2:为什么读操作时DRAM端需要关闭ODT,而控制器端启用?

A2:这是为了保证信号接收端的阻抗匹配,在读操作中,DRAM作为驱动端,若其ODT启用,相当于驱动端与终端电阻并联,会导致输出阻抗降低,信号幅度下降;而控制器端作为接收端,启用ODT可使传输线终端阻抗与接收输入阻抗匹配,消除反射,确保信号完整,若两端ODT同时启用,会形成并联低阻抗,导致信号畸变。