什么是电路板封装技术?

电路板封装技术 是指将制造好的半导体芯片(如CPU、GPU、内存颗粒等)和其它电子元器件,通过物理和电气方式,集成并保护起来,最终使其成为一个功能完整、可以独立安装和使用的电子模块的过程。

您可以把它想象成给脆弱的芯片“穿上盔甲、装上腿脚”:

- 芯片:是核心的大脑,非常脆弱,容易被静电、湿气、物理损伤破坏。

- 封装:就是这个“盔甲”和“腿脚”,它起到了以下关键作用:

- 物理保护:保护脆弱的硅芯片和内部的精细焊线。

- 电气连接:通过引脚、焊球等,将芯片的I/O(输入/输出)端口与外部电路板连接起来,实现信号和电力的传输。

- 散热管理:芯片工作时会产生大量热量,封装材料和结构需要将这些热量有效地引导出去,防止芯片过热烧毁。

- 尺寸优化:将芯片和必要的辅助元件集成在一个紧凑的空间内,减小最终产品的体积。

- 环境隔离:防止湿气、灰尘等有害物质侵入芯片内部。

封装技术的重要性

封装技术不仅仅是“打包”,它对整个电子产品的性能、成本、可靠性和尺寸有着决定性的影响。

- 性能瓶颈:随着芯片制程越来越先进(如7nm, 5nm),芯片内部的晶体管数量和运行频率急剧增加,芯片与封装之间的I/O数量和信号传输速度(带宽)成为新的瓶颈,先进的封装技术(如2.5D/3D封装)通过缩短连接距离,有效解决了这个问题。

- 散热挑战:高性能芯片的功耗巨大(如CPU、GPU功耗可达数百瓦),如何高效散热是设计的关键,封装技术直接决定了热量的传导路径和效率。

- 系统小型化:智能手机、可穿戴设备等对尺寸要求极为苛刻,封装技术允许将多个芯片、甚至无源元件(电阻、电容)集成在一起,实现高密度集成。

- 成本控制:封装是芯片制造流程中最后但成本占比很高的一环,封装技术的选择直接影响产品的最终成本和良率。

主流封装技术分类与发展

封装技术的发展史,就是一部不断追求更高集成度、更高性能、更小尺寸的历史。

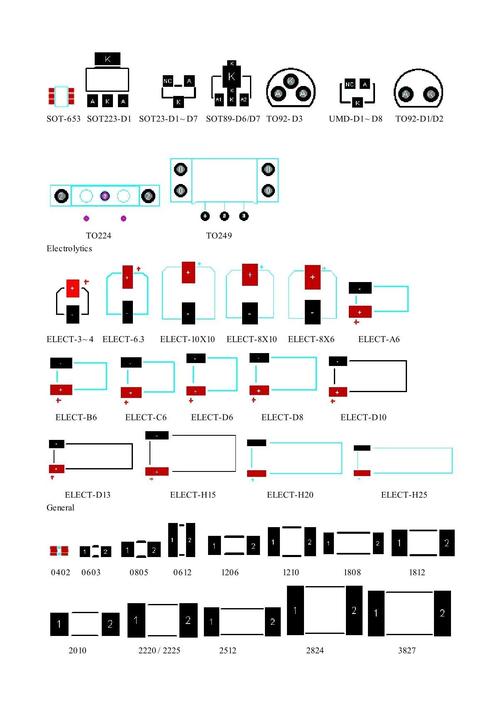

通孔插装技术 - “腿长”时代

这是早期的封装形式,元器件的引脚穿过PCB板上的孔进行焊接。

- DIP (Dual In-line Package):双列直插封装,最经典的封装,像有两条“长腿”。

- 特点:体积大,引脚数量少,易于手工焊接和维修。

- 应用:早期的内存条、CPU(如Intel 8086)。

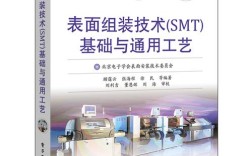

表面贴装技术 - “腿短”时代

引脚设计在封装的底部,直接贴在PCB表面进行焊接,这是现代电子技术的基础。

- SOP (Small Outline Package):小外形封装。

- QFP (Quad Flat Package):四侧引脚扁平封装,引脚更多更细。

- BGA (Ball Grid Array):球栅阵列封装,这是一个里程碑式的技术!

- 特点:用“焊球”阵列替代了引脚,实现了更高密度的I/O,散热更好,电气性能更优。

- 应用:现代CPU、GPU、内存条、FPGA等几乎所有高性能芯片都采用BGA或其变种。

系统级封装 - “打包箱”时代

SiP的核心思想是“将多个功能不同的芯片或元器件,像搭积木一样封装在一个封装体内,形成一个完整或接近完整的系统”。

- 特点:

- 高度集成:在一个封装内可以包含处理器、存储器、射频芯片、传感器等多个芯片。

- 异构集成:可以集成不同工艺、不同功能的芯片。

- 设计灵活:可以根据产品需求快速定制。

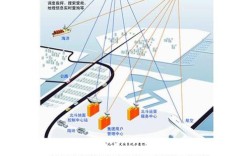

- 应用:智能手机里的射频模块、智能手表的核心模块、物联网设备。

先进封装 - “立体城市”时代

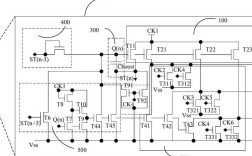

当摩尔定律逐渐放缓,先进封装成为延续摩尔定律、实现“超越摩尔”的关键路径,其核心是5D/3D集成。

-

5D 封装

(图片来源网络,侵删)

(图片来源网络,侵删)- 原理:像在一个平面上建“高楼”,但“楼”之间先通过一个“桥梁”(硅中介层,Interposer)连接好,再一起封装。

- 特点:中介层提供了极短、极密的布线通道,实现了芯片间的高速、高带宽连接。

- 典型代表:AMD的CPU/GPU组合(如Ryzen APU),将CPU核心和GPU核心通过硅中介层封装在一起,极大地提升了性能。

-

3D 封装

- 原理:像真正的“立体城市”,将芯片在垂直方向上堆叠起来,通过硅通孔技术实现层与层之间的直接电气连接。

- 特点:极致的集成度和带宽,最短的信号路径。

- 典型代表:

- HBM (High Bandwidth Memory):高带宽内存,是3D封装最成功的应用,将多个DRAM芯片堆叠在一起,通过TSV与GPU直接连接,提供远超传统内存的带宽。

- 手机SoC:很多手机处理器也采用3D封装,将NPU(神经网络处理单元)或RAM堆叠在主芯片之上。

-

其他前沿技术

- Chiplet (小芯片) / 2.5D/3D IC:这是当前最热门的方向,它将一个复杂的大型芯片(如SoC)分解成多个功能更专一、更小的“Chiplet”,分别用最优的工艺制造,然后通过先进封装技术(如硅中介层、混合键合)集成在一个封装内,这既能降低成本,又能提高良率和性能。

- 混合键合:比TSV更先进的技术,可以直接将芯片或晶圆的铜-铜键合,无需中介层,实现更高密度、更小尺寸的集成。

- 扇出型封装:将芯片的“引脚”直接从封装体上“扇出”,无需基板,成本更低,尺寸更小,广泛用于手机射频前端芯片。

封装技术的关键挑战与未来趋势

挑战

- 散热问题:高密度集成导致热量集中,如何设计高效的散热路径(如使用新型导热材料、嵌入式散热器)是巨大挑战。

- 信号完整性:随着I/O速率进入Gbps甚至更高,信号串扰、衰减、电磁干扰等问题愈发严重。

- 热机械应力:不同材料(硅、铜、有机基板)的热膨胀系数不同,在反复加热冷却过程中会产生应力,可能导致焊点开裂、分层等可靠性问题。

- 成本与良率:先进封装工艺极其复杂,设备昂贵,良率控制难度大,直接推高了成本。

- 测试与验证:封装完成后,如何对内部的复杂芯片系统进行有效的测试和故障诊断,是一个难题。

未来趋势

- 异构集成成为主流:将不同工艺、不同功能的芯片、无源元件、甚至光学元件集成在一起,将是未来系统设计的核心范式。

- “芯粒”生态的建立:Chiplet模式将推动一个标准化的“芯粒”生态,不同厂商可以设计和制造自己的“芯粒”,然后像搭乐高一样组合成定制化的高性能SoC。

- 新材料的应用:使用更低介电常数的封装材料、更高导热系数的散热材料(如金刚石、石墨烯)、以及新型基板材料来提升性能。

- 智能化与自动化:利用AI和大数据技术优化封装设计、预测良率、提高生产效率。

- 超越硅基的探索:研究如何将硅光子、氮化镓等第三代半导体技术与先进封装结合,实现更高性能的通信和电源管理。

电路板封装技术早已不是简单的“打包”,而是与芯片设计、制造同等重要的核心技术,它正从传统的平面保护,向着立体化、系统化、异构化的方向飞速发展,是驱动未来人工智能、5G/6G、物联网、高性能计算等前沿科技不断突破的关键引擎,理解封装技术,就是理解现代电子产品的灵魂所在。