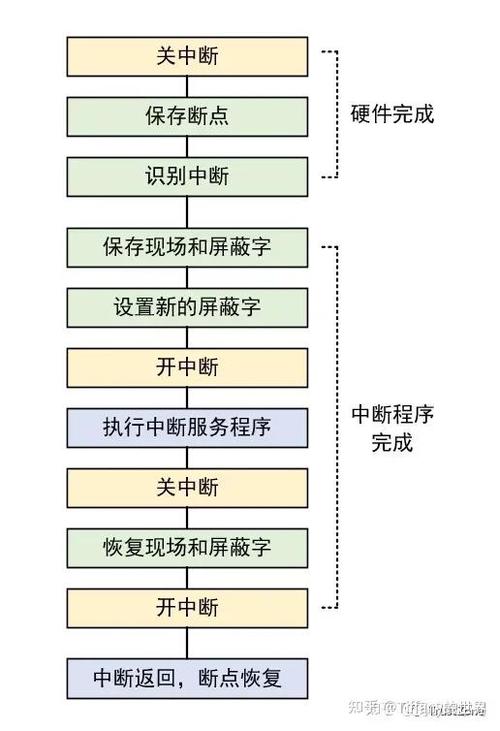

中断屏蔽技术是操作系统和嵌入式系统中管理中断的关键机制,其核心思想是通过暂时禁止某些或所有中断的响应,来保证特定代码段的原子性执行或满足实时性要求,中断屏蔽技术的利用并非随意为之,而是需要根据系统的具体场景、任务优先级和实时性需求来精准判断,以下从多个维度详细分析中断屏蔽技术的适用时机。

在操作系统的内核代码执行过程中,尤其是对共享数据或关键硬件资源进行访问时,中断屏蔽是必不可少的保护手段,在操作系统的调度程序中,当内核需要修改进程控制块(PCB)中的关键信息,如进程状态、优先级或上下文数据时,必须确保这些操作不被中断打断,如果在修改过程中发生中断,且中断处理程序同样访问或修改了PCB中的相同数据,就会导致数据不一致,引发系统崩溃或不可预期的行为,通过在进入临界区前屏蔽中断,并在退出临界区后解除屏蔽,可以确保相关代码段的原子性,类似地,在对内存管理中的页表、位图等全局数据结构进行修改时,也需要采用中断屏蔽技术,防止并发访问导致的数据损坏,这种场景下,中断屏蔽的持续时间通常很短,仅覆盖最核心的修改操作,以最大限度减少对系统响应时间的影响。

实时系统是中断屏蔽技术的重要应用领域,尤其是硬实时系统,其任务必须在严格规定的时间内完成,否则将导致系统失效,在硬实时任务执行期间,如果存在可能抢占该任务的中断,且这些中断的处理时间会超过任务的截止期限,就必须屏蔽这些中断,在工业控制系统中,一个需要周期性执行的运动控制任务,其每次执行必须在1毫秒内完成,如果系统中存在一个优先级较低但执行时间较长(如2毫秒)的中断源,且该中断未被屏蔽,那么它可能会在任务执行期间触发,导致任务无法按时完成,从而引发控制错误,通过在任务执行前屏蔽该中断,确保任务在无干扰的环境中运行,并在任务完成后解除屏蔽,可以满足实时性要求,需要注意的是,实时系统中的中断屏蔽必须谨慎设计,屏蔽的时间应尽可能短,且仅屏蔽与任务截止时间冲突的中断,避免因过度屏蔽导致其他重要中断得不到及时处理。

在设备驱动程序的开发中,中断屏蔽也常用于处理硬件同步问题,某些硬件设备在操作过程中需要与CPU进行严格的同步,在进行DMA传输时,CPU需要确保DMA控制器的配置参数完全写入后再启动传输,否则可能导致数据传输错误,驱动程序可以在配置参数前后屏蔽中断,防止其他中断打断配置过程,在处理某些硬件中断时,如果中断服务程序(ISR)需要执行较长时间的操作,或者需要访问与主程序共享的临界资源,也可能在ISR内部临时屏蔽中断,以避免嵌套中断导致的数据竞争或栈溢出问题,在一个网络驱动程序中,当ISR接收数据包并需要将其拷贝到内核缓冲区时,如果此时有另一个硬件中断(如定时器中断)发生,且该ISR也访问相同的缓冲区,就可能造成数据混乱,通过在关键拷贝操作期间屏蔽中断,可以确保数据的一致性。

嵌入式系统中,对中断的精细化管理是优化系统性能的关键,在某些资源受限的嵌入式设备中,为了降低中断延迟或减少中断处理的开销,可能会采用中断屏蔽技术来合并中断或批量处理事件,在一个数据采集系统中,多个传感器可能通过同一个中断线向CPU发送数据就绪信号,如果每个传感器的中断都立即触发ISR,那么频繁的中断切换会消耗大量CPU时间,可以在主程序中屏蔽传感器中断,当系统空闲时再解除屏蔽,一次性处理所有待处理的中断事件,从而提高系统的整体效率,在嵌入式系统的启动初始化阶段,为了完成硬件的初始化配置(如设置时钟、配置GPIO等),通常需要屏蔽所有中断,以确保初始化过程的完整性和正确性,避免在初始化过程中发生意外中断导致系统不稳定。

中断屏蔽技术的利用还需要考虑系统的中断优先级机制,在支持可编程中断控制器(PIC)的高级中断控制器中,中断通常具有不同的优先级,中断屏蔽不仅可以屏蔽所有中断,还可以仅屏蔽低于或等于某个优先级的中断,从而允许高优先级的中断仍然能够得到响应,这种分级屏蔽机制在实时系统中尤为重要,它可以在保证关键任务执行的同时,仍然允许处理一些高优先级的紧急事件,在一个航空电子系统中,飞行控制任务可能屏蔽所有低于“关键”级别的中断,但仍允许“紧急”级别的中断(如发动机故障告警)触发,从而在保证核心任务执行的同时,不遗漏重要的异常情况。

需要注意的是,中断屏蔽技术的滥用会带来严重的负面影响,过度屏蔽中断会导致系统响应时间变长,甚至丢失重要的中断事件,尤其是在高负载系统中,在设计中断屏蔽策略时,必须遵循“最小化屏蔽时间”和“精准屏蔽”的原则,即仅在绝对必要时才屏蔽中断,且屏蔽的范围应尽可能小,仅覆盖必要的临界区,应避免在用户态代码中使用中断屏蔽,除非有特殊的实时性要求且经过严格验证,在内核态,中断屏蔽的使用也应受到严格控制,通常与自旋锁、信号量等其他同步机制结合使用,以确保系统的安全性和稳定性。

| 应用场景 | 具体时机 | 潜在风险与注意事项 |

|---|---|---|

| 内核临界区保护 | 修改共享数据结构(如PCB、页表)时 | 屏蔽时间过长导致系统响应延迟;需确保临界区代码简洁高效 |

| 硬实时任务执行 | 任务截止期限短,存在可能抢占的中断时 | 过度屏蔽可能丢失高优先级中断;需精确计算中断屏蔽时间与任务执行时间的关系 |

| 设备驱动程序同步 | DMA配置、硬件参数写入、ISR中访问共享资源时 | 可能导致硬件操作失败或数据竞争;需结合硬件手册设计屏蔽逻辑 |

| 嵌入式系统初始化 | 硬件启动阶段,完成关键配置时 | 初始化完成后需及时解除屏蔽,避免影响后续中断处理 |

| 中断事件批量处理 | 低优先级中断合并处理,减少中断切换开销时 | 可能增加中断延迟;需权衡批量处理效率与实时性要求 |

相关问答FAQs:

Q1:中断屏蔽技术是否会影响系统的实时性?

A1:是的,中断屏蔽会影响系统的实时性,其影响程度取决于屏蔽的范围和持续时间,屏蔽所有中断会导致所有中断响应被延迟,可能使高优先级中断错过截止期限;而仅屏蔽低优先级中断则可以在保证关键任务执行的同时,允许高优先级中断及时响应,在实时系统中,必须精确计算中断屏蔽时间,并采用分级屏蔽策略,以最小化对实时性的负面影响。

Q2:如何在用户态程序中使用中断屏蔽技术?

A2:在大多数操作系统中,用户态程序无法直接屏蔽中断,因为中断屏蔽是内核态的特权操作,如果用户态程序有特殊的实时性需求,通常需要通过系统调用请求内核提供服务,例如使用实时线程(如POSIX的SCHED_FIFO或SCHED_RR调度策略),并让内核在适当的时候执行中断屏蔽,某些嵌入式系统的实时操作系统(RTOS)可能提供允许用户态任务临时屏蔽中断的API,但这需要确保用户态代码的可靠性,避免因错误使用导致系统崩溃,一般情况下,不建议在用户态随意使用中断屏蔽技术,而应优先使用同步原语(如互斥锁、信号量)来保护共享资源。