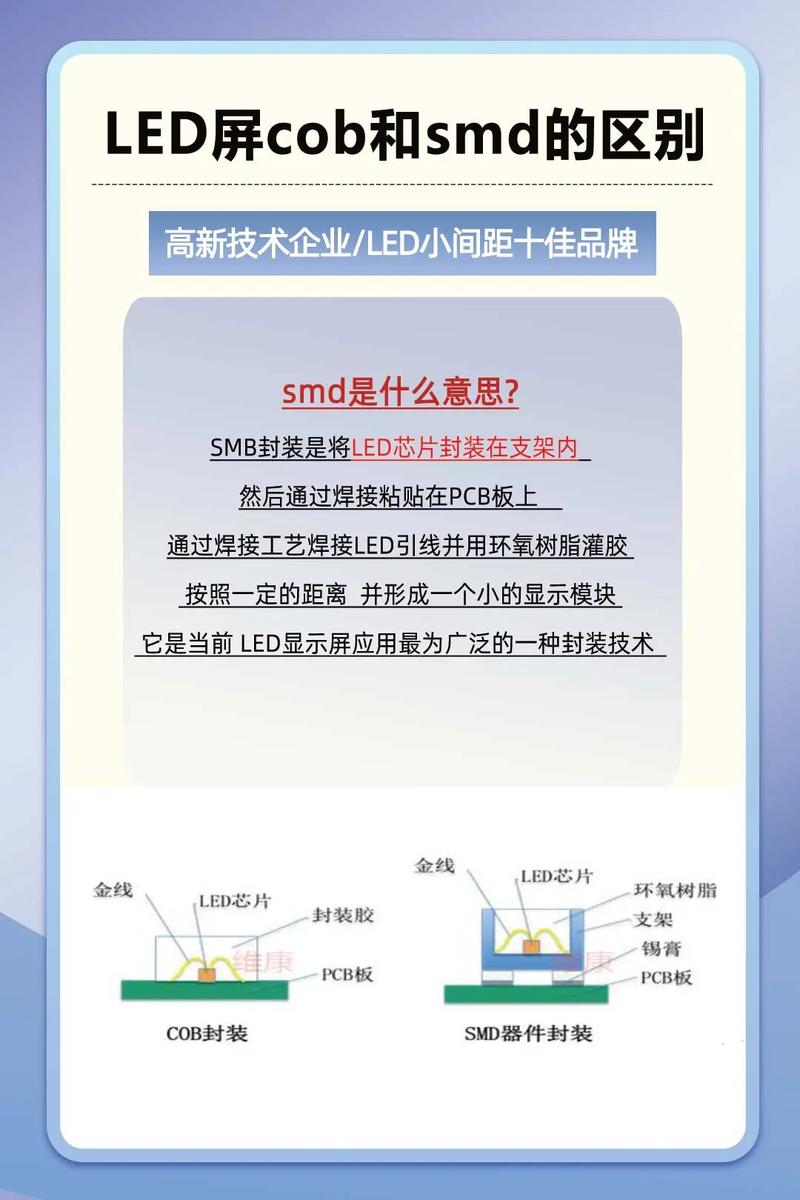

COB封装技术中的点间距是衡量芯片集成密度和显示性能的关键指标,直接决定了显示设备的分辨率、清晰度以及应用场景的适配性,点间距通常指相邻两个发光单元(如LED芯片或Micro LED)中心之间的距离,单位为毫米(mm),数值越小,代表单位面积内的像素点数量越多,显示效果越细腻,在COB(Chip On Board,板上芯片)封装技术中,点间距的设计与实现需要结合芯片尺寸、封装工艺、基板材料以及驱动电路等多方面因素,其技术难点和解决方案也随着显示行业对高分辨率、高画质需求的提升而不断演进。

从技术原理来看,COB封装的点间距优化首先依赖于芯片微缩技术,传统LED芯片尺寸较大,点间距难以缩小到1.0mm以下,而随着Mini LED和Micro LED技术的发展,芯片尺寸从百微米级向十微米级迈进,为点间距的缩小提供了基础,当芯片尺寸从100μm×100μm缩小到20μm×20μm时,在相同封装密度下,点间距可从1.5mm降至0.4mm以下,但芯片微缩也带来了 challenges:一是芯片的巨量转移精度要求更高,需确保数万甚至数百万颗芯片准确贴合到基板的焊盘上,误差需控制在±5μm以内;二是小尺寸芯片的散热性能下降,需通过优化封装结构(如采用高导热系数的基板材料、增加散热通道)来避免光衰和寿命缩短。

封装基板的设计是影响点间距的另一核心因素,COB封装常用的基板材料包括FR-4、铝基板、陶瓷基板以及近年来的柔性PI基板等,不同基板的线宽、线间距能力直接影响点间距的实现极限,传统FR-4基板的线宽/线间距通常大于75μm,难以支持0.4mm以下的点间距;而采用半加成法(SAP)工艺的柔性PI基板可实现30μm/30μm的精细线路,满足0.3mm甚至0.15mm点间距的需求,基板的厚度和平整度也至关重要,尤其是在高密度封装中,基板的弯曲变形可能导致芯片偏移或焊接不良,因此需选用低热膨胀系数(CTE)的材料,并通过多层结构设计来增强机械稳定性。

驱动电路的集成方式与点间距密切相关,在COB封装中,驱动芯片可以采用外置、集成或嵌入式三种方案:外置方案驱动芯片位于显示模组周边,适用于点间距较大的场景(如1.0mm以上),但会缩小有效显示区域;集成方案将驱动芯片与像素芯片共同封装在基板上,可缩短信号传输路径,提升响应速度,适合0.5-1.0mm点间距;嵌入式方案则将驱动电路直接制作在基板内部,实现更高密度的集成,是支持0.3mm以下超小点间距的关键技术,嵌入式方案对基板的层数和布线复杂度要求极高,需通过高密度互连(HDI)技术甚至硅通孔(TSV)工艺来实现,这显著增加了制造成本。

散热管理是COB封装中点间距缩小面临的重要难题,当点间距减小时,单位面积内的芯片数量增加,功率密度急剧上升,若散热不良会导致局部温度过高,引发芯片光效下降、色偏甚至失效,为解决这一问题,行业普遍采用以下技术路径:一是优化封装结构,如使用倒装芯片(Flip-Chip)技术替代正装芯片,减少热量通过焊料层传导的路径;二是采用高导热界面材料(如导热硅胶、石墨烯膜)填充芯片与基板之间的空隙;三是设计微流道散热系统,通过液体冷却方式快速带走热量,在0.4mm点间距的COB显示屏中,结合倒装芯片和微流道散热技术,可使模组工作温度控制在60℃以下,确保长时间稳定运行。

点间距还直接影响COB封装的良率和成本,随着点间距缩小,基板布线密度、芯片转移精度、焊接工艺要求均呈指数级提升,导致生产难度加大,不良率上升,0.3mm点间距COB模组的良率可能比0.8mm产品低20%-30%,从而推单颗像素成本,为降低成本,行业正在探索巨量转移新技术(如激光转移、自组装转移)、自动化光学检测(AOI)以及修复工艺,通过提高生产效率和降低不良率来缩小小间距COB的市场价格差距。

以下是不同点间距COB封装技术的关键参数对比:

| 点间距(mm) | 芯片尺寸(μm) | 基板类型 | 驱动方案 | 典型应用场景 | 成本等级 |

|---|---|---|---|---|---|

| 0-1.5 | 100×100-200×200 | FR-4/铝基板 | 外置驱动 | 商业显示、户外广告 | 中低 |

| 5-0.8 | 50×50-100×100 | 陶瓷基板/柔性PI | 集成驱动 | 高端商业显示、会议系统 | 中高 |

| 3-0.4 | 20×20-50×50 | 多层柔性PI/HDI | 嵌入式驱动 | 虚拟拍摄、医疗显示 | 高 |

| <0.2 | <20×20 | 硅基板/TSV | 全集成驱动 | AR/VR、微显示 | 极高 |

相关问答FAQs:

-

问:COB封装的点间距越小,是否一定代表显示效果越好?

答:并非绝对,点间距越小,像素密度越高,近距离观看时画面越细腻,这是优势,但需结合实际应用场景:在大型户外显示屏中,过小的点间距可能导致观看距离过近时出现像素颗粒感,且成本过高;而在室内近距离观看的高端显示场景(如控制室、医疗影像),小间距COB能显著提升细节表现力,点间距缩小还需配合更高的灰度等级、刷新率和色彩校准技术,否则可能因驱动能力不足导致画面卡顿或色差。 (图片来源网络,侵删)

(图片来源网络,侵删) -

问:COB封装实现超小点间距(如0.15mm以下)面临的最大技术瓶颈是什么?

答:超小点间距COB封装的核心瓶颈在于“巨量转移精度”与“散热-集成度平衡”,0.15mm点间距意味着每平方米需集成数千万颗Micro LED芯片,目前主流的激光转移技术精度可达±3μm,但仍难以满足亿级芯片的零缺陷转移需求;芯片尺寸缩小至10μm级后,散热面积急剧减少,而驱动电路的集成又进一步限制了散热空间,需通过硅基集成、TSV等先进技术将驱动芯片与像素芯片三维堆叠,但这又会引入热耦合问题,需综合设计散热结构和封装材料才能突破。