FPGA数字移相技术是现代数字信号处理和通信系统中的核心环节,它利用现场可编程门阵列(FPGA)的高速并行处理能力和丰富的逻辑资源,实现对信号相位的精确控制,相较于传统的模拟移相网络,基于FPGA的数字移相技术具有精度高、稳定性好、可重构性强以及易于集成等显著优势,广泛应用于相控阵雷达、波束成形、软件无线电以及精密测量仪器等领域。

从本质上讲,数字移相是对数字信号在时间域或频率域上进行操作,从而改变其相位特性,在FPGA中实现数字移相主要有三种主流技术路线:基于数控振荡器(NCO/DDS)的移相、基于延时链的移相以及基于CORDIC算法的移相,这三种方法在原理、资源占用和应用场景上各有千秋。

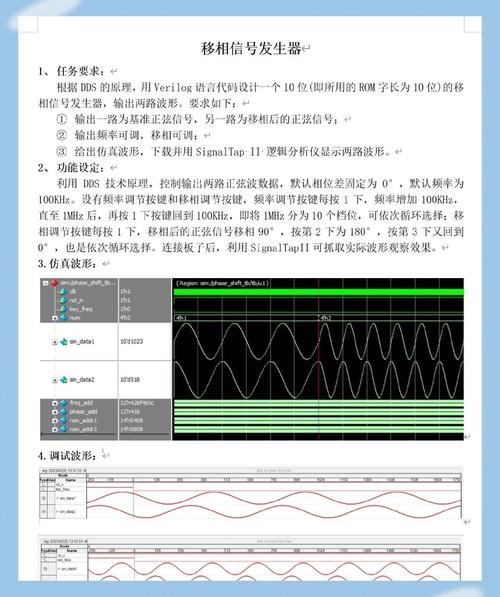

基于数控振荡器(NCO)或直接数字频率合成(DDS)的移相方法是最为常见且灵活的方案,其核心原理是利用相位累加器生成瞬时相位,再通过查表或近似算法生成正弦波,若要实现移相,只需在相位累加器的输出端增加一个相位偏置值,在一个32位的相位累加器中,若需要移相90度,只需在当前相位值上加上2^30(即总相位范围的1/4),这种方法的精度极高,理论上仅受限于相位累加器的位宽,可以达到微弧度级别,在FPGA实现中,通常会使用Block RAM(BRAM)来存储正弦查找表(LUT),或者利用DSP Slice进行多项式拟合,该方案特别适用于通信系统中的载波同步和本振信号生成,因为它不仅能移相,还能极其方便地调整频率。

基于延时链的数字移相技术主要应用于时钟信号或高速串行数据的相位调整,这种方法不改变信号的数据内容,而是通过物理或逻辑上的延迟单元,改变信号到达的时间点,在FPGA内部,这种技术常用于DDR控制器接口或高速ADC数据采集的时序对齐,具体实现手段包括使用专用的时钟管理单元(如Xilinx的MMCM或Intel的PLL),这些硬核IP可以动态调整输出时钟的相位,步长通常在几十皮秒量级,还可以利用FPGA内部的进位链或级联逻辑构建抽头延迟线,通过控制信号经过的逻辑门数量来实现亚纳秒级的延时调整,这种方法对于解决高速电路中的建立时间和保持时间违规问题至关重要。

第三,基于CORDIC(坐标旋转数字计算机)算法的移相技术则是处理复数信号和基带信号的利器,CORDIC算法是一种迭代算法,它仅通过移位和加法运算,就能实现向量旋转,从而完成复数的乘法操作,在实现数字下变频(DDC)或波束成形算法时,经常需要将信号乘以e^(jθ),这正是CORDIC算法的专长,相比于使用大量乘法器的FFT或直接复数乘法,CORDIC算法对FPGA中的DSP Slice资源消耗极少,主要消耗逻辑资源(LUT),虽然它有一定的流水线延迟,但在处理连续数据流时吞吐率很高,非常适合在雷达信号处理机中实现多通道的实时相位加权。

为了更直观地对比这三种技术,可以参考下表:

| 移相技术方案 | 核心原理 | 精度表现 | 资源消耗 | 主要应用场景 |

|---|---|---|---|---|

| NCO/DDS查表法 | 相位累加器加偏置,查ROM表 | 极高(取决于位宽) | 消耗BRAM和少量逻辑 | 信号发生器、载波同步、调制解调 |

| 延时链/MMCM | 调整信号传输延迟时间 | 中等(受限于器件工艺) | 消耗专用时钟资源或LUT | 时钟相位调整、时序对齐、高速接口 |

| CORDIC算法 | 迭代矢量旋转运算 | 高(取决于迭代次数) | 消耗大量LUT,不占DSP | 波束成形、坐标变换、复数解调 |

在实际的FPGA工程开发中,数字移相技术的实现面临着若干挑战与优化需求,首先是相位噪声的问题,由于FPGA系统时钟是离散的,且受限于晶振抖动和电源噪声,数字合成信号的相位噪声往往优于模拟方案,但在超高速应用中仍需仔细设计时钟网络,在DDS实现中,相位截断误差会引入杂散,这需要通过抖动注入技术来改善信号质量。

资源与速度的平衡,以CORDIC算法为例,虽然它节省了昂贵的DSP资源,但其迭代结构决定了每一级迭代都会产生一级流水线延迟,如果系统对实时性要求极高(例如纳秒级响应的雷达防御系统),可能需要展开迭代循环,但这会成倍增加逻辑资源的使用,工程师通常需要在VHDL或Verilog代码中进行参数化设计,根据实际需求权衡迭代级数和时钟频率。

多通道同步也是FPGA数字移相的关键难点,在相控阵雷达或有源天线系统中,可能需要同时控制几十甚至上百个通道的相位,FPGA内部必须维护一套精确的相位控制寄存器组,并通过统一的系统参考时钟来触发更新,以确保所有通道的相位变化是同步发生的,任何通道间的相位不一致都会导致波束指向误差或信号增益下降。

FPGA数字移相技术是一个融合了数字信号处理理论与硬件逻辑设计的综合性领域,随着FPGA工艺制程向7nm及更先进节点发展,以及高速收发器速率的不断提升,数字移相的精度和带宽正在不断突破物理极限,从简单的逻辑延时到复杂的算法实现,FPGA为工程师提供了强大的工具箱,使得相位的数字化控制变得前所未有的灵活和精确。

相关问答FAQs

Q1: 在FPGA中实现数字移相时,DDS(直接数字频率合成)的相位截断误差是什么?它对信号有什么影响?

A1: DDS的相位截断误差是由于FPGA硬件资源有限,无法使用相位累加器的所有位来寻址查找表(ROM)而产生的,一个32位的相位累加器可能只有高14位用于查表,低18位被截断,这种截断会导致输出信号的相位出现周期性的微小跳变,从而在输出频谱中产生杂散信号,降低信号的无杂散动态范围(SFDR),为了减小这种影响,工程师通常会增加查表地址的位宽,或者使用相位抖动技术,通过引入随机噪声来打散固定的杂散分量,从而提升频谱纯度。

Q2: 为什么在波束成形应用中,CORDIC算法比直接使用复数乘法器更受欢迎?

A2: 在波束成形的移相操作中,主要涉及复数与旋转因子的乘法(即 $e^{j\theta}$),虽然使用FPGA内部的DSP Slice可以实现高速复数乘法,但在大规模多通道系统中,DSP资源往往非常紧缺(通常用于滤波或FFT),CORDIC算法只需要移位和加法器即可实现矢量旋转,不需要昂贵的乘法器资源,在资源受限且对绝对延迟要求不是极端苛刻的场景下,使用CORDIC算法可以大幅节省FPGA成本,并留出更多DSP资源给系统中的其他关键算法使用。