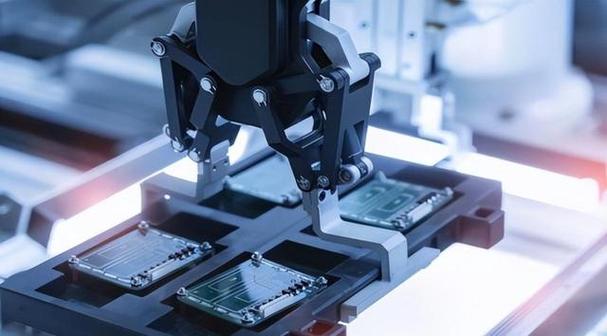

DRAM生产制造技术是半导体产业中最为复杂和精密的领域之一,其核心在于通过一系列高度专业化的工艺步骤,在硅晶圆上构建出数十亿个存储单元,以实现数据的快速读写与存储,这一过程融合了材料科学、光学、化学、物理学等多学科尖端技术,每一个环节的精度与效率都直接影响最终产品的性能、成本及良率,以下将从晶圆制造、核心工艺、技术挑战及未来趋势等方面,详细阐述DRAM的生产制造技术。

DRAM的生产始于硅晶圆的制备,高纯度单晶硅是制造DRAM的基础材料,通过直拉法或区熔法将多晶硅熔化后拉制成圆柱形的单晶硅锭,再经过切割、研磨、抛光等工序,形成厚度均匀、表面光滑的硅晶圆,主流DRAM晶圆尺寸已从12英寸(300mm)向18英寸(450mm)过渡,更大的晶圆尺寸能够在一次生产中制造更多芯片,有效降低单位成本,晶圆表面的平整度要求极高,任何微小的瑕疵都可能导致后续工艺失败,因此抛光工艺需达到纳米级的精度。

接下来是晶圆制造的核心环节——光刻工艺,光刻技术如同“印刷术”,将电路图案转移到晶圆表面,在晶圆表面旋涂一层光刻胶,通过掩模版(Mask)将紫外极紫外(EUV)光照射到光刻胶上,使其发生化学反应,再通过显影液溶解特定区域的光刻胶,形成所需的电路图形,随着DRAM存储单元不断微缩,光刻技术也从193nm深紫外(DUV)演进到EUV工艺,EUV光源波长仅为13.5nm,能够实现7nm及以下制程的精细图案,是解决摩尔定律延续难题的关键,EUV设备价格高昂、技术复杂,且对生产环境洁净度要求极高(需达到Class 10或更高标准),这显著增加了DRAM的制造成本。

光刻之后,是刻蚀、薄膜沉积、离子注入等一系列反复循环的工艺步骤,刻蚀工艺利用等离子体或化学反应,去除未被光刻胶保护的材料,将电路图案精确转移到硅层;薄膜沉积则通过化学气相沉积(CVD)或物理气相沉积(PVD)技术,在晶圆表面生长绝缘层、导电层(如电极)等;离子注入则是将掺杂离子(如硼、磷)加速后注入硅片,以改变半导体材料的导电类型,形成PN结等关键结构,这些工艺需要精确控制温度、压力、气体流量等参数,确保薄膜厚度均匀性、刻蚀各向异性(避免侧向腐蚀)等指标达标,在DRAM电容制造中,需要通过高深宽比刻蚀技术形成深沟槽,再通过原子层沉积(ALD)技术逐层生长高介电常数材料(如HfO₂),以提升存储容量。

DRAM的核心在于其存储单元结构,传统1T1C(1个晶体管+1个电容)结构中,电容的存储密度直接决定了DRAM的容量,随着制程微缩至10nm以下,电容的物理尺寸急剧缩小,为保持存储电荷能力,必须采用创新的电容结构,如深沟槽电容(Trench Capacitor)或堆叠式电容(Stacked Capacitor),深沟槽电容将电容嵌入硅衬底中,利用垂直空间增加存储面积;堆叠式电容则在晶体管上方构建多层电容结构,进一步节省平面空间,高k金属栅(HKMG)技术的应用也有效降低了栅极漏电流,提升了晶体管开关性能。

在完成所有前道工艺后,晶圆进入后道工序,包括晶圆测试、切割、封装和测试,通过探针台对晶圆上的每个芯片进行功能测试,筛选出合格芯片;使用精密锯片将晶圆切割成单个芯片;封装工艺则将芯片封装在保护壳中,并引出电极引脚,使其能够与电路板连接,DRAM封装技术从传统的TSOP(薄型小尺寸封装)发展到先进的BGA(球栅阵列封装)、FOWLP(扇型晶圆级封装)等,后者通过封装体内部布线缩短信号传输路径,提升高频性能,同时减小封装尺寸,满足移动设备对小型化的需求。

DRAM生产制造面临着诸多技术挑战,首先是良率控制,随着晶圆尺寸增大和制程微缩,工艺复杂性呈指数级增长,任何微小的污染或参数偏差都可能导致芯片失效,因此需要引入先进的缺陷检测技术(如光学扫描显微镜、电子束检测)和实时工艺监控系统,其次是成本控制,18英寸晶圆设备、EUV光刻机等投资动辄数亿美元,且研发周期长,这要求厂商通过规模效应和工艺优化摊薄成本,存储单元的漏电流问题也日益突出,当电容尺寸缩小到纳米级别时,量子隧穿效应会导致电荷快速泄漏,影响数据保持时间,这需要通过新型材料(如二维材料)和结构创新(如负电容晶体管)来解决。

未来DRAM技术将向更高密度、更低功耗、更高速度方向发展,在存储架构方面,通过3D堆叠技术(如高带宽内存HBM的多层堆叠)进一步提升存储容量和带宽;在材料方面,探索铁电材料(FeRAM)或磁阻材料(MRAM)与DRAM的结合,以突破传统电容的物理极限;在制造工艺方面,极紫外光刻(EUV)的成熟应用将推动制程向5nm及以下节点迈进,同时人工智能驱动的工艺优化技术将提升生产效率和良率,存算一体架构的探索也可能改变传统DRAM的数据处理模式,减少数据搬运带来的能耗延迟。

以下是相关问答FAQs:

Q1: DRAM生产中,为什么EUV光刻技术如此重要?

A1: EUV光刻技术是DRAM实现先进制程(7nm及以下)的核心,随着DRAM存储单元微缩,传统193nm DUV光刻技术通过多重曝光等方式已接近物理极限,不仅成本高昂,且难以满足更高精度的图形需求,EUV光源波长(13.5nm)更短,能够直接实现更高分辨率、更少曝光步骤的图形转移,显著提升芯片性能和降低复杂度,采用EUV技术后,DRAM的线宽可以进一步缩小,存储单元密度得以提升,同时减少工艺步骤,提高生产效率,尽管EUV设备昂贵且维护复杂,但它是延续摩尔定律、实现DRAM技术迭代的关键工具。

Q2: DRAM的“1T1C”结构是什么,其在技术演进中面临哪些挑战?

A2: “1T1C”是DRAM最基本的存储单元结构,1T”指1个晶体管,用于控制数据的读写;“1C”指1个电容,用于存储电荷,晶体管作为开关,电容的电荷状态(有电荷表示“1”,无电荷表示“0”)代表数据,这种结构简单可靠,但随着制程微缩,面临两大挑战:一是电容尺寸缩小导致存储电荷能力下降,数据易丢失;二是平面空间有限,难以继续提升存储密度,为解决这些问题,业界开发了深沟槽电容(利用垂直空间)和堆叠式电容(在晶体管上方多层堆叠)等创新结构,并通过引入高k介电材料(如HfO₂)提升电容密度,同时探索新型存储架构(如3D集成)以突破平面限制。