音乐VHDL程序技术是一种将音乐理论与数字电路设计相结合的先进技术,它利用硬件描述语言(VHDL)在可编程逻辑器件(如FPGA或CPLD)上实现音乐相关的功能,如音符生成、和弦处理、节奏控制等,这种技术结合了数字信号处理、逻辑设计和音乐算法,能够高效地实现复杂的音乐系统,常用于电子乐器、音乐合成器、音频处理设备等领域,VHDL作为一种硬件描述语言,具有并行处理能力强、时序控制精确、可移植性好等特点,非常适合用于音乐系统的硬件实现。

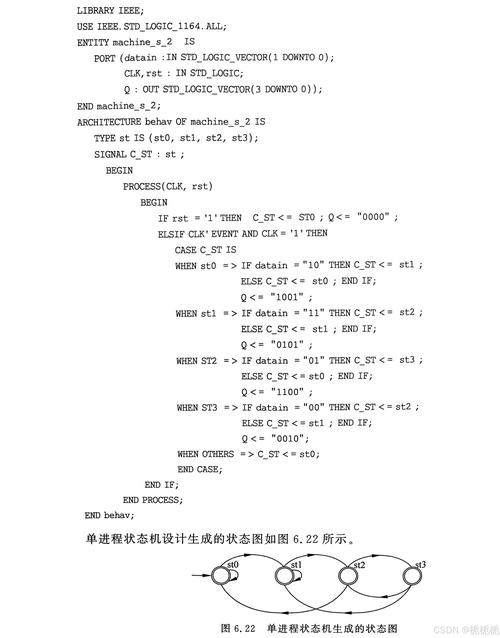

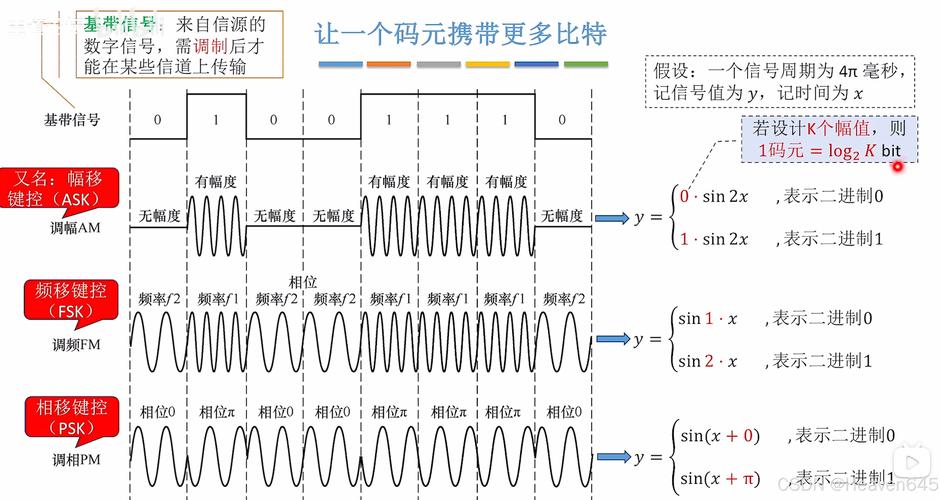

音乐VHDL程序的核心在于音符和节奏的数字化表示,在数字系统中,音符通常通过频率来定义,例如标准音A4的频率为440Hz,VHDL程序可以通过计数器或直接数字频率合成(DDS)技术生成特定频率的方波、正弦波或其他波形,从而模拟不同乐器的音色,节奏控制则需要精确的时钟分频和状态机设计,确保音符的持续时间符合乐谱要求,一个4/4拍的乐曲可以通过状态机控制不同音符的播放顺序,同时结合计数器实现节拍的时间控制。

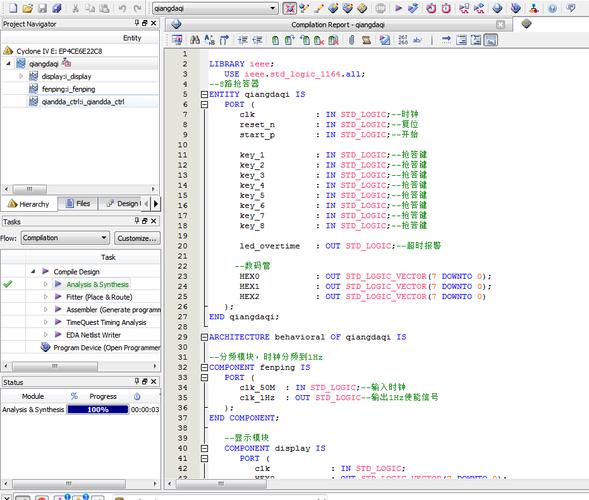

在技术实现层面,音乐VHDL程序通常采用模块化设计,包括音符发生器、节奏控制器、波形选择器和输出接口等模块,音符发生器负责根据输入的音符代码生成对应的频率信号,可以通过查找表(LUT)或DDS算法实现,节奏控制器则通过状态机管理音符的切换和休止符的处理,确保乐曲的连贯性,波形选择器允许用户选择不同的波形类型(如正弦波、方波、锯齿波),以模拟不同乐器的音色,输出模块则将数字信号转换为模拟信号,通过数模转换器(DAC)或直接驱动扬声器。

以下是一个简单的音符发生器VHDL代码示例,展示了如何通过计数器生成不同频率的方波:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity NoteGenerator is

Port (

clk : in STD_LOGIC; -- 系统时钟

note : in INTEGER range 0 to 127; -- 音符代码(0-127)

output : out STD_LOGIC -- 输出方波

);

end NoteGenerator;

architecture Behavioral of NoteGenerator is

signal counter : INTEGER range 0 to 1000000 := 0;

signal frequency : INTEGER := 440; -- 默认频率(A4)

begin

process(clk)

begin

if rising_edge(clk) then

-- 根据音符代码设置频率(示例:仅支持部分音符)

case note is

when 60 => frequency <= 262; -- C4

when 62 => frequency <= 294; -- D4

when 64 => frequency <= 330; -- E4

when 65 => frequency <= 349; -- F4

when 67 => frequency <= 392; -- G4

when 69 => frequency <= 440; -- A4

when 71 => frequency <= 494; -- B4

when others => frequency <= 440;

end case;

-- 生成方波

if counter < (100000000 / frequency / 2) then

output <= '1';

else

output <= '0';

end if;

counter <= counter + 1;

if counter >= (100000000 / frequency) then

counter <= 0;

end if;

end if;

end process;

end Behavioral;

该代码通过计数器生成特定频率的方波,音符代码与频率的对应关系可以通过扩展查找表实现更复杂的音符映射,在实际应用中,还需要结合节拍控制器和波形选择模块,以实现完整的音乐播放功能。

音乐VHDL程序技术的优势在于其高实时性和可定制性,与软件实现相比,硬件实现能够避免软件延迟,确保音符的精确播放,VHDL设计的模块化特性使得系统易于扩展和升级,例如添加音效处理、多声道支持等功能,FPGA的并行处理能力可以同时处理多个音符和声部,实现复杂的音乐合成。

该技术也存在一定挑战,VHDL设计需要深厚的数字电路和时序分析知识,调试过程相对复杂,硬件资源的限制(如逻辑单元数量、存储容量)可能影响系统的功能实现,在设计音乐VHDL程序时,需要合理规划资源分配,优化算法效率。

以下是一个简单的模块化设计表格,展示了音乐VHDL程序的主要模块及其功能:

| 模块名称 | 功能描述 |

|---|---|

| 音符发生器 | 根据输入音符代码生成对应频率的数字信号 |

| 节奏控制器 | 通过状态机管理音符切换和休止符处理,确保节奏正确 |

| 波形选择器 | 选择不同波形类型(正弦波、方波等),模拟不同乐器音色 |

| 输出接口 | 将数字信号转换为模拟信号,或直接驱动扬声器 |

| 时钟分频器 | 生成系统所需的多种时钟频率,支持不同音符和节拍的精确控制 |

相关问答FAQs:

-

问:音乐VHDL程序与软件音乐播放器有何区别?

答:音乐VHDL程序是基于硬件的实现,运行在FPGA或CPLD等可编程逻辑器件上,具有并行处理能力强、实时性高的特点,能够精确控制音符的时序和频率,而软件音乐播放器通常运行在CPU上,依赖软件算法生成音频信号,可能存在延迟和资源占用问题,硬件实现更适合需要高精度和低延迟的音乐应用,如电子乐器和实时音频处理。 -

问:如何优化音乐VHDL程序的资源占用? | 答:优化资源占用可以从以下几个方面入手:一是采用模块化设计,复用公共模块(如时钟分频器);二是使用查找表(LUT)替代复杂的计算逻辑,减少逻辑单元的使用;三是合理分配时序资源,避免不必要的时钟域转换;四是采用流水线设计,提高并行处理效率,可以通过综合工具分析资源占用情况,针对瓶颈模块进行优化,确保系统在有限资源下实现最佳性能。