FPGA与EDA技术是现代电子设计领域的核心组成部分,它们相互依存、相互促进,共同推动了数字系统设计的快速发展,FPGA(现场可编程门阵列)作为一种半定制集成电路,以其灵活性、高并行性和可重构性,在通信、工业控制、人工智能、医疗设备等领域得到了广泛应用;而EDA(电子设计自动化)技术则是支撑FPGA设计全流程的关键工具链,涵盖了从算法建模、逻辑综合、物理设计到验证测试的各个环节,两者的结合不仅大幅提升了设计效率,还降低了开发成本,成为现代电子系统不可或缺的技术支撑。

FPGA的出现源于对传统ASIC(专用集成电路)设计周期长、灵活性不足的改进需求,与ASIC不同,FPGA允许用户在硬件层面进行编程,通过重新配置内部逻辑单元、布线资源和输入输出模块,实现不同的功能,这种“硬件可重构”特性使得FPGA在原型验证、快速迭代和小批量生产中具有独特优势,随着制程工艺的进步,现代FPGA已从简单的逻辑门阵列发展为集成处理器核心、高速收发器、大容量存储器和专用硬件加速器的高度集成化平台,Xilinx的Zynq系列和Intel的Cyclone 10 GX系列FPGA,不仅包含ARM处理器内核,还支持PCIe、以太网等高速接口,能够满足复杂SoC(片上系统)的设计需求。

EDA技术则是实现FPGA设计的必要工具,它通过计算机辅助设计手段,将设计者的抽象描述转化为可实现的硬件电路,FPGA设计流程通常包括以下几个阶段,每个阶段都依赖EDA工具的支持:首先是设计输入阶段,工程师可以使用硬件描述语言(如VHDL、Verilog)或高级建模工具(如SystemC)描述系统功能;其次是功能仿真阶段,通过ModelSim、Xcelium等工具验证逻辑设计的正确性;然后是逻辑综合阶段,利用Synopsys Design Compiler或Vivado综合工具将行为级描述转换为逻辑门级网表;接下来是布局布线阶段,通过FPGA厂商提供的专用工具(如Quartus Prime、Vivado)将网表映射到FPGA的物理资源上,并完成时序优化;最后是时序仿真和板级验证阶段,确保设计在实际工作环境中的性能符合要求。

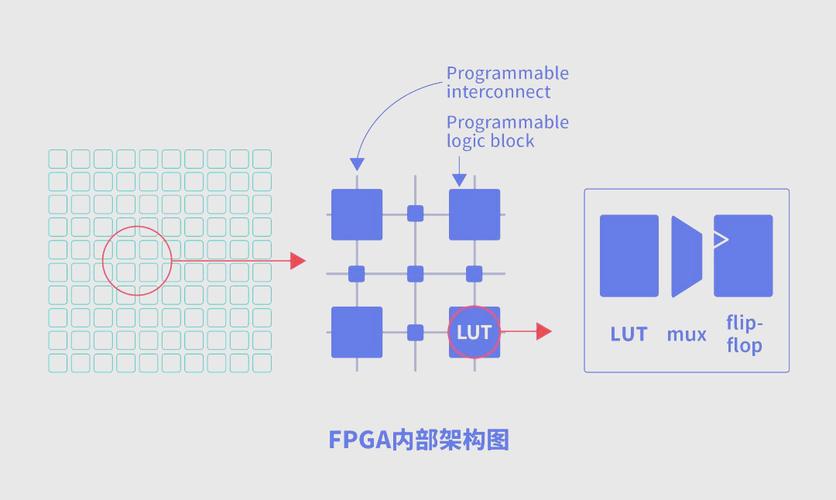

在FPGA设计中,EDA工具的选择直接影响设计效率和结果质量,以逻辑综合为例,综合工具需要根据FPGA的架构特性优化代码,例如合理利用查找表(LUT)、触发器(FF)等资源,避免不必要的逻辑冗余,对于高性能设计,时序分析工具(如TimeQuest)能够精确计算路径延迟,帮助工程师解决建立时间(Setup Time)和保持时间(Hold Time)违例问题,随着FPGA规模不断扩大,功耗分析工具(如Power Analyzer)也成为必备,通过动态功耗和静态功耗的估算,帮助优化系统散热设计。

FPGA与EDA技术的结合还推动了设计方法的革新,传统设计流程中,工程师需要手动编写RTL代码并进行多次迭代,而现代EDA工具支持高级综合(HLS),允许使用C/C++或Python描述算法,自动生成RTL代码,大幅提升了复杂算法的设计效率,在人工智能领域,Xilinx Vitis AI和Intel OpenVINO工具链支持将深度学习模型直接部署到FPGA上,通过HLS优化神经网络运算,实现低延迟的推理加速,基于云的EDA平台(如AWS FPGA Cloud、Alibaba Cloud FPGA)提供了远程编译和仿真服务,降低了硬件资源限制,使中小企业也能享受高性能FPGA设计工具。

为了更直观地展示FPGA设计流程中EDA工具的应用,以下表格列举了各阶段常用工具及其功能:

| 设计阶段 | 常用EDA工具 | 主要功能 |

|---|---|---|

| 设计输入 | Vivado、Quartus Prime、ModelSim | 支持VHDL/Verilog/SystemC代码编写与语法检查 |

| 功能仿真 | ModelSim、Xcelium、Questa | 验证设计逻辑功能,仿真行为级和RTL级模型 |

| 逻辑综合 | Synopsys DC、Vivado Synthesis | 将RTL代码转换为门级网表,优化资源利用和时序 |

| 布局布线 | Vivado P&R、Quartus Fitter | 将网表映射到FPGA物理资源,完成布局布线和时序优化 |

| 时序分析 | TimeQuest、PrimeTime | 分析路径延迟,检查时序约束,解决建立/保持时间违例 |

| 功耗分析 | Power Analyzer、PTPX | 估算动态功耗和静态功耗,提供功耗优化建议 |

| 高级综合 | Xilinx Vitis HLS、Intel HLS | 将C/C++代码自动转换为RTL代码,加速算法设计 |

| 板级验证 | LabVIEW、SignalTap | 通过逻辑分析仪和示波器功能,调试硬件信号与系统行为 |

FPGA与EDA技术的发展也面临诸多挑战,随着工艺节点进入7nm及以下,FPGA的物理设计复杂性急剧增加,EDA工具需要解决信号完整性、电源完整性等高级问题;AIoT(人工智能物联网)的兴起对FPGA的低功耗、小尺寸提出了更高要求,EDA工具需要支持异构计算和系统级优化,设计安全性和知识产权保护也成为关注重点,部分EDA工具已开始集成加密和防篡改功能。

展望未来,FPGA与EDA技术的融合将更加深入,量子计算、边缘计算等新兴领域将推动FPGA向更高性能、更低功耗方向发展,而EDA工具则需要适应新的设计范式,例如支持量子算法建模、3D IC设计等,人工智能技术本身也将被应用于EDA流程,通过机器学习优化布局布线算法,提升设计自动化水平,可以预见,FPGA与EDA技术的持续创新将为电子产业带来更多可能性,助力数字化转型浪潮。

相关问答FAQs:

-

问:FPGA与ASIC的主要区别是什么?为什么选择FPGA而不是ASIC?

答:FPGA是现场可编程的,允许用户在设计完成后重新配置功能,适合快速原型验证、小批量生产或需要频繁更新的场景;而ASIC是定制化的,一旦流片就无法修改,适合大规模量产且需求固定的产品,选择FPGA的主要原因是其灵活性高、开发周期短、前期投入成本低,尤其适合迭代频繁的设计;而ASIC的优势在于高性能、低功耗和单位成本低,但需要承担较高的设计流片费用和风险。 -

问:EDA工具在FPGA设计中是否必不可少?能否完全用手工设计替代?

答:EDA工具在FPGA设计中几乎是必不可少的,现代FPGA规模庞大(数千万至数十亿逻辑门),手工设计不仅效率极低,而且难以保证时序和功能的正确性,EDA工具通过自动化流程(如综合、布局布线、时序分析)大幅提升设计效率和可靠性,虽然简单的逻辑模块可能通过手工描述实现,但对于复杂系统(如SoC、高速接口),完全依赖手工设计几乎不可行,且容易引入错误,EDA工具是FPGA设计的核心支撑。