DMA访问的技术原理主要涉及硬件与软件的协同工作机制,通过专用控制器实现外设与内存之间的直接数据传输,减少CPU干预,提升系统效率,其核心在于绕过CPU的数据搬运过程,让外设和内存通过总线直接交换数据,同时确保数据传输的准确性和系统的稳定性。

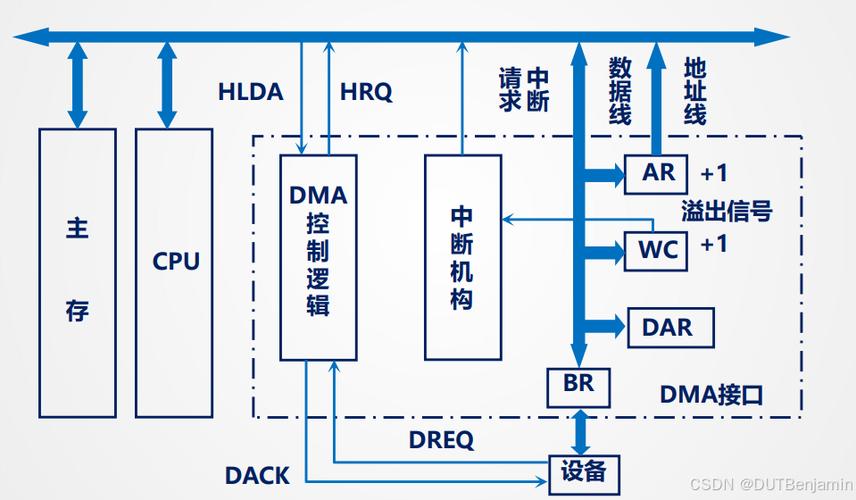

从硬件架构来看,DMA控制器(DMAC)是实现DMA访问的关键组件,DMAC内部包含多个功能模块,如地址寄存器、数据计数器、控制状态寄存器和仲裁逻辑等,地址寄存器用于存储当前传输的内存起始地址,在每次传输后自动递增或递减,指向下一个数据单元;数据计数器记录待传输的数据量,每完成一次传输后减1,当计数器归零时触发传输完成中断;控制状态寄存器则配置传输方向(内存到外设或外设到内存)、传输模式(单次传输、块传输、请求传输等)以及中断使能等状态;仲裁逻辑负责协调多个DMA请求的优先级,避免总线冲突,DMAC需要与系统总线(如AMBA、PCIe等)和外设接口紧密连接,通过总线信号(如请求REQ、允许ACK等)与外设和CPU交互。

软件层面,DMA的启动过程需要驱动程序初始化DMAC的参数,驱动程序需分配目标内存缓冲区,并确保其物理地址连续(部分DMA控制器支持分散-列表模式,可处理非连续内存),配置DMAC的控制寄存器,设置源地址(外设寄存器地址或内存地址)、目标地址(内存地址或外设寄存器地址)、传输数据量、传输宽度(字节/半字/字)以及传输方向,当网卡需要接收数据时,驱动程序会将DMAC的源地址设置为网卡的接收缓冲区寄存器地址,目标地址设置为系统内存中预分配的缓冲区地址,并启动传输,外设(如网卡)检测到数据就绪后,向DMAC发送DMA请求信号(REQ),DMAC在获得总线控制权后,直接将数据从外设搬运至内存,无需CPU参与。

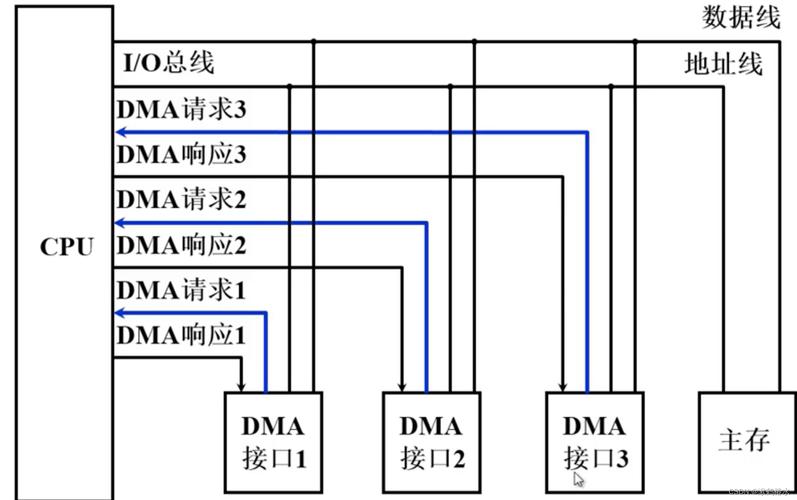

总线控制权的切换是DMA访问的核心环节,在CPU正常执行程序时,系统总线由CPU控制;当DMAC接收到外设的REQ信号后,需向总线仲裁器(如总线矩阵)发起总线请求(BUSRQ),仲裁器根据预设的优先级策略(如固定优先级、轮转优先级等)判断是否允许总线请求,若当前总线空闲或允许抢占,仲裁器会向CPU发送总线响应(BUSACK),通知CPU释放总线控制权;CPU响应后将总线地址线、数据线和控制线的管理权交给DMAC,DMAC获得总线控制权后,开始执行数据传输:通过地址总线选定目标内存单元,通过数据总线传输数据,并通过控制总线发出读写信号,每次传输完成后,DMAC更新地址寄存器和数据计数器,直到数据计数器归零,传输结束后,DMAC释放总线控制权,并向CPU发送中断信号(IRQ),通知CPU数据传输已完成,此时CPU可继续处理其他任务。

为确保数据传输的正确性,DMA机制采用了多种同步与校验机制,在传输过程中,DMAC会与外设通过握手信号(如外设的“数据就绪”和DMAC的“数据接收”)保持同步,避免数据丢失或覆盖,对于高速外设(如SSD、网卡),通常会采用 burst(突发)传输模式,即在一次总线占用中连续传输多个数据单元,减少总线切换开销,提高传输效率,部分DMA控制器支持 scatter-gather(分散-收集)模式,允许将多个不连续的内存地址组合成一个传输列表,DMAC按顺序遍历列表完成数据传输,适用于需要处理分散数据的应用场景(如网络数据包重组),在安全性方面,现代DMA控制器还集成了访问权限控制机制,限制DMA只能访问预先授权的内存区域,防止恶意外设非法篡改系统内存。

DMA的应用场景广泛,几乎涉及所有需要高速数据传输的外设,在存储系统中,SATA控制器通过DMA将硬盘数据直接传输到内存;在图形处理中,GPU通过DMA进行显存与系统内存之间的数据交换;在网络通信中,网卡利用DMA实现数据包的接收和发送,大幅降低CPU负载,DMA也存在一定的局限性,如总线带宽竞争可能导致系统性能下降,以及DMA传输过程中若发生错误(如内存地址越界),可能引发系统崩溃,在设计DMA系统时,需合理规划总线优先级,并增加错误检测与恢复机制。

相关问答FAQs:

-

Q:DMA与PIO(Programmed I/O)的主要区别是什么?

A:PIO模式下,CPU需要通过指令逐字节或逐字读取外设数据并写入内存,全程占用CPU资源,效率较低;而DMA模式下,数据传输由DMAC硬件直接控制,CPU只需在传输开始和结束时参与,无需干预具体数据搬运过程,大幅提升系统吞吐量并降低CPU占用率,在PIO模式下,网卡每接收一个数据包都需要CPU多次参与读写操作;而在DMA模式下,网卡只需发起一次DMA请求,即可完成整个数据包的传输。 -

Q:DMA传输过程中如何避免总线冲突?

A:DMA通过总线仲裁机制解决总线冲突问题,当多个外设同时发起DMA请求时,总线仲裁器会根据预设的优先级策略(如固定优先级或轮转优先级)决定哪个DMAC获得总线控制权,高优先级的外设请求会优先被响应,低优先级请求则需等待,现代系统通常采用多层总线架构(如SoC中的总线矩阵),将不同模块的DMA请求分配到独立的总线通道,减少竞争,在ARM架构中,AXI总线矩阵支持多主多从设备,可动态分配总线带宽,确保DMA传输与其他系统活动并行进行,避免冲突。 (图片来源网络,侵删)

(图片来源网络,侵删)