Cache优化技术是提升计算机系统性能的核心手段之一,通过减少数据访问延迟、降低带宽压力,显著改善应用程序的响应速度和整体效率,随着数据量激增和计算复杂度提升,cache优化技术已从简单的硬件缓存扩展到多层次、智能化的综合解决方案,涵盖硬件设计、算法策略、软件协同等多个维度,以下从cache层次结构、替换算法、预取技术、写策略、数据一致性及软件优化等方面展开详细分析。

多层次cache架构优化

现代计算机系统通常采用多级cache架构(L1、L2、L3),各级cache在容量、速度和成本上存在差异,优化需平衡三者关系,L1 cache(分为L1d和L1i,分别存储数据和指令)容量最小(通常为32-64KB),但速度最快(1-2周期访问),优化重点在于减少访问冲突和提升命中率,通过调整cache行大小(如从64B增至128B),可减少指令或数据的频繁换入换出,但需避免行过载导致空间浪费,L2 cache容量适中(256KB-1MB),速度次之(约10周期),常作为L1与主存的缓冲,优化时可采用非包容性设计(即L1与L2允许重复数据),或通过动态分区技术为不同任务分配缓存资源,L3 cache(统一共享,容量可达32MB以上)速度较慢(约40-50周期),但能被多核心共享,优化重点在于降低核心间数据竞争,如采用目录协议维护一致性,或通过NUMA架构优化跨节点访问延迟。

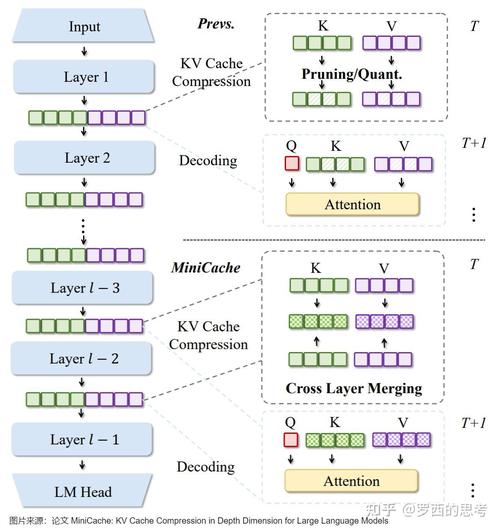

cache替换算法优化

当cache满载时,需替换现有数据以容纳新数据,替换算法直接影响命中率,传统算法如LRU(最近最少使用)实现简单,但在特定场景下性能不佳(如循环访问或批量数据时可能误删活跃数据),优化方向包括:

- 分层LRU(LRU-K):记录数据最近K次访问时间,减少短时数据对长时数据的干扰,例如LRU-2通过区分“最近访问”和“历史访问”,提升对循环数据的适应性。

- 动态算法(如ARC、2Q):结合LRU和LFU(最不经常使用)的优点,ARC(Adaptive Replacement Cache)维护LRU和LFU两个队列,根据访问模式动态调整权重,适用于数据库等混合负载场景。

- 机器学习驱动算法:通过训练模型预测数据访问概率(如基于历史访问序列的LSTM模型),实现智能替换,在复杂工作负载中可较LRU提升10%-20%命中率。

cache预取技术优化

预取通过提前将可能需要的数据加载到cache中,减少等待时间,预取策略可分为:

- 指令预取:在取指阶段预测下一条指令流,如分支目标缓冲(BTB)记录分支历史,提前预取分支目标指令,减少分支惩罚。

- 数据预取:根据访问模式触发预取,如stride预取(根据连续访问间隔预测下次地址),适用于数组遍历;stream预取(识别连续数据流)适用于媒体处理。

- 智能预取:结合硬件与软件协同,例如操作系统通过页面访问历史预取内存页,或GPU通过纹理访问模式预取纹理数据,预取需避免过度预取导致cache污染,可通过设置预取队列深度(如4-8条)或动态调整预取触发阈值优化。

写策略优化

写策略决定数据何时写回主存,直接影响数据一致性和性能。

- 写直达(Write-Through):数据同时写入cache和主存,确保数据一致性,但增加内存带宽压力,适用于对一致性要求高的场景(如实时系统)。

- 写回(Write-Back):仅更新cache,仅在数据被替换时写回主存,减少内存访问,但需配合脏位标记(Dirty Bit)管理,优化点包括延迟写回(合并多次写操作)或写分配(Write-Allocate,写未命中时加载主存块到cache),后者适合频繁修改数据的场景(如缓存行中的元数据更新)。

- 混合策略:如写穿透+写缓存(Write-Through with Write Buffer),利用缓冲队列暂存写操作,减少直接内存访问次数。

数据一致性与缓存优化

在多核/多节点系统中,cache一致性协议(如MESI、MOESI)是关键优化点,MESI协议通过标记cache行状态(Modified、Exclusive、Shared、Invalid)避免脏数据回写冲突,但总线事务开销较大,优化方向包括:

- 目录协议(Directory Protocol):替代总线嗅探,通过集中式目录记录数据分布,减少广播式一致性维护,适用于大规模多核心系统(如服务器芯片)。

- 一致性优化:如采用“所有权”机制(某核心拥有数据修改权限),减少无效化广播;或通过延迟确认(Lazy Acknowledgment)合并一致性操作,降低总线负载。

软件层面的cache优化

软件优化可显著提升cache利用率,核心是减少cache冲突和未命中:

- 数据结构对齐:将热点数据按cache行大小对齐(如64B/128B),避免跨行访问导致的伪共享(False Sharing),在多线程场景中,将不同线程的数据分配到不同cache行,减少核心间数据冲突。

- 循环优化:通过循环分块(Loop Tiling)改善数据局部性,将大循环拆分为小块,使数据在cache中重复使用,矩阵乘法中按块(如64×64)处理,而非逐行或逐列遍历。

- 缓存感知算法:设计算法时考虑cache容量,如B树索引的节点大小适配L1 cache,减少磁盘访问;或使用缓存友好的数据结构(如跳表替代平衡树)。

- 编译器优化:利用编译器指令(如

__builtin_prefetch)显式预取数据,或通过自动向量化(Auto-vectorization)提升数据访问连续性。

特定场景下的cache优化

| 场景 | 优化技术 | 效果 |

|---|---|---|

| 高并发数据库 | 无锁数据结构(如LSM树)、多级预取(索引+数据页) | 减少锁竞争,提升事务处理速度20%-30% |

| AI/深度学习 | 张量缓存(Tensor Cache)、权重预加载、NUMA感知分配 | 减少GPU-CPU数据传输延迟,提升训练效率15%-25% |

| 实时嵌入式系统 | 固定分区cache(时间分区)、静态预取、指令缓存锁定 | 确保任务执行时间可预测,延迟波动<5% |

| 大数据分析 | 列式存储(如Parquet)、缓存感知shuffle(MapReduce) | 提升数据扫描效率,减少磁盘I/O 40%以上 |

相关问答FAQs

Q1:为什么多核系统中伪共享会降低cache性能?如何避免?

A1:伪共享指多个核心同时访问同一cache行中的不同数据,导致cache一致性协议频繁触发(如核心1修改数据后,核心2的cache行需失效),即使数据无逻辑关联,线程A和B分别访问变量X和Y(位于同一cache行),X的修改会导致Y的缓存失效,避免方法包括:

- 数据填充(Padding):在变量间填充无意义数据(如

struct { int x; char pad[60]; int y; }),确保热点数据位于不同cache行。 - 缓存行分离:将频繁修改的数据分配到独立cache行,或使用编程语言特性(如C++的

alignas(64))强制对齐。

Q2:cache预取技术可能带来哪些问题?如何优化预取准确性?

A2:预取的主要问题包括:

- cache污染:预取的数据未被使用,挤占活跃数据空间,降低整体命中率。

- 带宽浪费:预取不必要的数据增加内存/总线负载,尤其在低带宽场景下。

优化方法: - 动态阈值调整:根据cache命中率动态调整预取触发条件(如命中率低于80%时暂停预取)。

- 上下文感知预取:结合程序语义(如循环边界、函数调用)预取,而非仅依赖地址模式。

- 预取过滤:利用机器学习模型预测数据访问概率,仅对高概率数据预取,减少无效预取。