linear技术支持作为电子设计自动化(EDA)领域的重要组成部分,为工程师提供了从芯片设计到验证的全流程解决方案,其核心在于通过高效的算法和工具链,帮助用户实现复杂逻辑电路的快速设计与优化,尤其在FPGA(现场可编程门阵列)和ASIC(专用集成电路)设计中发挥着不可替代的作用,以下将从技术架构、核心功能、应用场景及支持服务等多个维度,详细阐述linear技术支持的实现路径与价值。

技术架构与核心功能

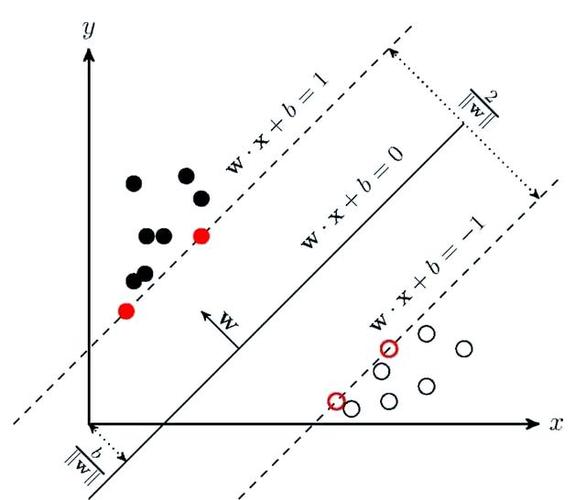

linear技术支持体系以模块化设计为基础,涵盖前端设计、逻辑综合、布局布线、时序分析及验证等关键环节,其技术架构可分为硬件描述语言(HDL)支持层、逻辑优化层、物理实现层及验证调试层四大部分,在HDL支持层,工具兼容Verilog、VHDL等主流硬件描述语言,并提供语法检查、代码规范自动修正等功能,帮助工程师减少语法错误,提升代码质量,逻辑优化层则基于先进的布尔代数简化技术和状态机优化算法,通过逻辑等价变换、冗余逻辑消除等手段,降低电路复杂度,提升芯片性能。

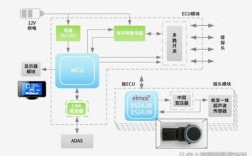

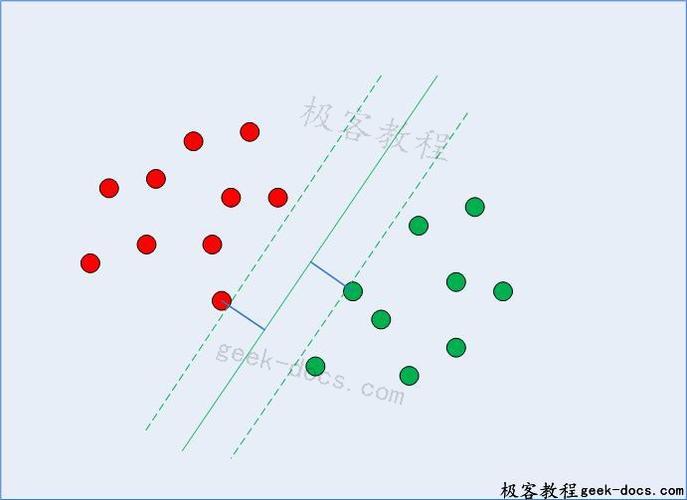

物理实现层是linear技术支持的核心,其布局布线算法采用多目标优化策略,同时考虑时序、功耗和面积(PPA)三大指标,在FPGA设计中,工具可根据器件架构自动规划逻辑单元、布线资源及IO引脚分配,并通过迭代优化减少关键路径的时序裕量,针对ASIC设计,支持标准单元库与工艺角(Process Corner)的联合优化,确保设计在不同工艺条件下的稳定性,时序分析模块支持静态时序分析(STA)和动态时序分析,能快速定位建立时间(Setup Time)和保持时间(Hold Time)违例,并提供时序约束优化建议。

应用场景与行业实践

linear技术支持广泛应用于通信、汽车电子、工业控制及消费电子等领域,以5G基站设计为例,其基带处理单元需要实现高并行度的信号处理算法,linear技术支持的逻辑综合工具可自动将复杂的数学运算映射为FPGA的查找表(LUT)和分布式RAM结构,并通过流水线优化提升数据吞吐量,在汽车电子领域,功能安全(ISO 26262)标准对芯片的可靠性要求极高,linear技术支持提供故障注入分析和冗余设计验证功能,帮助工程师满足ASIL(Automotive Safety Integrity Level)等级要求。

针对不同设计规模,linear技术支持提供了差异化解决方案,对于千万门级以上的复杂SoC(System on Chip),其分布式计算架构支持多节点并行处理,可将布局布线时间从传统的数天缩短至数小时,而在中小规模FPGA设计中,轻量版工具集则通过资源占用优化,支持在低配置硬件环境中运行,满足嵌入式开发的需求。

技术支持服务体系

linear技术支持不仅提供工具软件,还构建了完善的技术服务体系,其在线支持平台包含知识库、案例库及社区论坛,工程师可快速检索常见问题解决方案,如HDL代码优化技巧、时序收敛方法等,针对企业用户,linear提供定制化培训服务,内容涵盖从基础操作到高级优化策略的全流程课程,帮助团队提升设计效率,紧急响应机制则通过全球技术支持网络,确保在重大设计问题出现时,能在4小时内提供专家级远程支持。

linear技术支持还与主流晶圆厂和FPGA厂商建立深度合作,提供针对特定工艺节点或器件架构的优化模型,与台积电合作提供7nm工艺的时序库文件,与Xilinx合作优化UltraScale+系列的布局布线算法,确保设计在目标平台上实现最佳性能。

性能优化与行业趋势

随着芯片制程不断向7nm及以下节点推进,设计复杂度呈指数级增长,linear技术支持也在持续迭代,在算法层面,引入机器学习技术,通过历史数据训练布局布线预测模型,提升优化效率,在工具集成方面,支持与Python、Tcl等脚本语言联动,实现设计流程的自动化定制,工程师可通过编写Python脚本批量修改时序约束,或利用Tcl命令驱动工具完成多轮迭代优化。

linear技术支持将向云端化和智能化方向发展,云平台部署模式支持按需付费的计算资源调度,降低中小企业使用门槛;而AI驱动的智能调试功能则能自动识别设计瓶颈,并提供修复建议,进一步缩短设计周期。

相关问答FAQs

Q1: linear技术支持是否支持低代码或无代码设计模式?

A1: 是的,linear技术支持最新版本提供了图形化设计界面,支持通过拖拽方式搭建逻辑电路,并自动生成HDL代码,该功能主要面向初学者或简单逻辑设计场景,可大幅降低设计门槛,但对于复杂算法或高性能设计,仍建议使用传统HDL编码方式以实现更精细的控制。

Q2: 在使用linear技术支持进行多FPGA协同设计时,如何解决跨芯片时序同步问题?

A2: 针对多FPGA协同设计,linear技术支持提供了全局时序分析(Global Timing Analysis)模块,该模块通过统一的时钟约束和跨芯片时序报告,可识别不同FPGA之间的时钟偏斜(Clock Skew)和数据传输延迟,具体解决方案包括:使用全局时钟分配网络、调整源同步接口的时序参数,或插入FIFO缓冲器来吸收时序差异,工具内置的“时序收敛助手”功能还能自动生成优化建议,帮助工程师快速完成跨芯片时序同步。